- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385404 > HT82K95E (Holtek Semiconductor Inc.) USB Multimedia Keyboard Encoder 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT82K95E |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | USB Multimedia Keyboard Encoder 8-Bit MCU |

| 中文描述: | 的USB多媒體鍵盤(pán)編碼器8位微控制器 |

| 文件頁(yè)數(shù): | 20/48頁(yè) |

| 文件大小: | 319K |

| 代理商: | HT82K95E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

HT82K95E/HT82K95A

Rev. 1.20

20

October 24, 2005

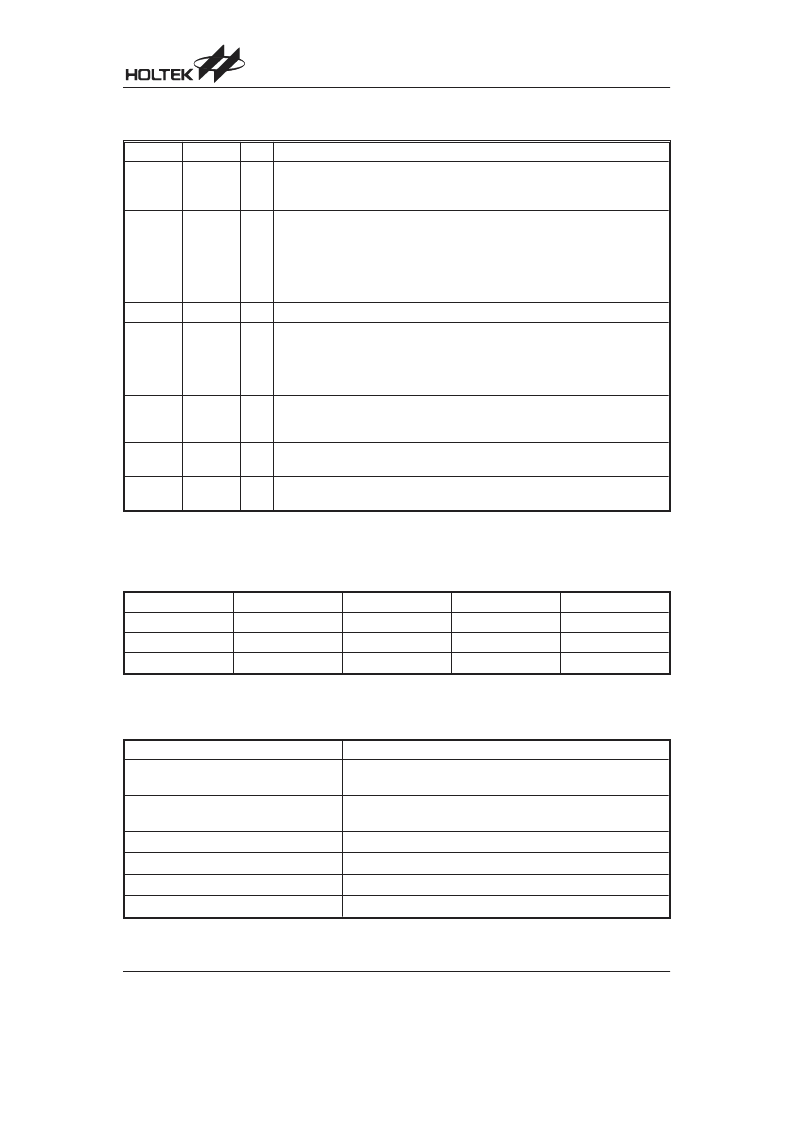

MISC register combines a command and status to control desired endpoint FIFO action and to show the status of the

desired endpoint FIFO. The MISC will be cleared by USB reset signal.

Bit No.

Label

R/W

Function

0

REQ

R/W

After setting the other status of the desired one in the MISC, endpoint FIFO can be

requested by setting this bit to 1 . After the job has been done, this bit has to be

cleared to 0 .

1

TX

R/W

This bit defines the direction of data transferring between MCU and endpoint FIFO.

When the TX is set to 1 , this means that the MCU wants to write data to the end-

point FIFO. After the job has been done, this bit has to be cleared to 0 before termi-

nating request to represent the end of transferring. For reading action, this bit has to

be cleared to 0 to represent that MCU wants to read data from the endpoint FIFO

and has to be set to 1 after the job is done.

2

CLEAR

R/W

Clear the requested endpoint FIFO, even if the endpoint FIFO is not ready.

4

3

SELP1

SELP0

R/W

Defines which endpoint FIFO is selected, SELP1,SELP0:

00: endpoint FIFO0

01: endpoint FIFO1

10: endpoint FIFO2

11: reserved

5

SCMD

R/W

Used to show that the data in endpoint FIFO is a SETUP command. This bit has to

beclearedbyfirmware.Thatistosay,eventheMCUisbusy,thedevicewillnotmiss

any SETUP commands from the host.

6

READY

R

Read only status bit, this bit is used to indicate that the desired endpoint FIFO is

ready to work.

7

LEN0

R/W

Used to indicate that a 0-sized packet is sent from a host to the MCU. This bit should

be cleared by firmware.

MISC (46H) Register

The MCU can communicate with the endpoint FIFO by setting the corresponding registers, of which address is listed in

the following table. After reading the current data, next data will show after 2 s, used to check the endpoint FIFO status

and response to MISC register, if read/write action is still going on.

Registers

R/W

Bank

Address

Bit7~Bit0

FIFO0

R/W

1

48H

Data7~Data0

FIFO1

R/W

1

49H

Data7~Data0

FIFO2

R/W

1

4AH

Data7~Data0

There are some timing constrains and usages illustrated here. By setting the MISC register, MCU can perform reading,

writing and clearing actions. There are some examples shown in the following table for endpoint FIFO reading, writing

and clearing.

Actions

MISC Setting Flow and Status

Read FIFO0 sequence

00H

check not ready (01H)

01H

delay 2 s, check 41H

read* from FIFO0 register and

03H

02H

Write FIFO1 sequence

0AH

check not ready (0BH)

0BH

delay 2 s, check 4BH

09H

write* to FIFO1 register and

08H

Check whether FIFO0 can be read or not

00H

01H

delay 2 s, check 41H (ready) or 01H (not ready)

00H

Check whether FIFO1 can be written or not

0AH

0BH

delay2 s,check4BH(ready)or0BH(notready)

0AH

Read 0-sized packet sequence form FIFO0

00H

01H

delay 2 s, check 81H

read once (01H)

03H

02H

Write 0-sized packet sequence to FIFO1

0AH

0BH

delay 2 s, check 0BH

0FH

0DH

08H

Note:

*: There are 2 s existing between 2 reading action or between 2 writing action

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82K96A | USB Multimedia Keyboard Encoder 8-Bit Mask MCU |

| HT82K96E | 8-Bit USB Multimedia Keyboard Encoder OTP MCU |

| HT82M21A | 3-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22 | 5-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22A | 5-Key 3D USB+PS/2 Optical Mouse Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82K95EE | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Multimedia Keyboard Encoder 8-Bit MCU |

| HT82K96A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Multimedia Keyboard Encoder 8-Bit Mask MCU |

| HT82K96E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit USB Multimedia Keyboard Encoder OTP MCU |

| HT82K96E_07 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Multimedia Keyboard Encoder 8-Bit OTP MCU |

| HT82M13 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Mouse/Trackball Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。