- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385403 > HT82A821R (Holtek Semiconductor Inc.) USB Audio MCU PDF資料下載

參數(shù)資料

| 型號: | HT82A821R |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | USB Audio MCU |

| 中文描述: | USB音頻控制器 |

| 文件頁數(shù): | 16/39頁 |

| 文件大小: | 275K |

| 代理商: | HT82A821R |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

HT82A821R

Rev. 1.10

16

June 29, 2007

USB Interface

The HT82A821R have 3 Endpoints (EP0 ~EP2). EP0 supports Control transfer. EP1 supports Interrupt transfer. EP2

supports Isochronous transfer.

These registers, including USC (20H), USR (21H), UCC (22H), AWR (23H), STALL (24H ), SIES (25H), MISC (26H),

SETIO (27H), FIFO0 (28H), FIFO1 (29H), FIFO2 (2AH) used for the USB function.

The FIFO size of each FIFO is 8 byte (FIFO0), 8 byte (FIFO1), 384 byte (FIFO2), and total are 400 bytes.

URD (bit7 of USC) is USB reset signal control function definition bit.

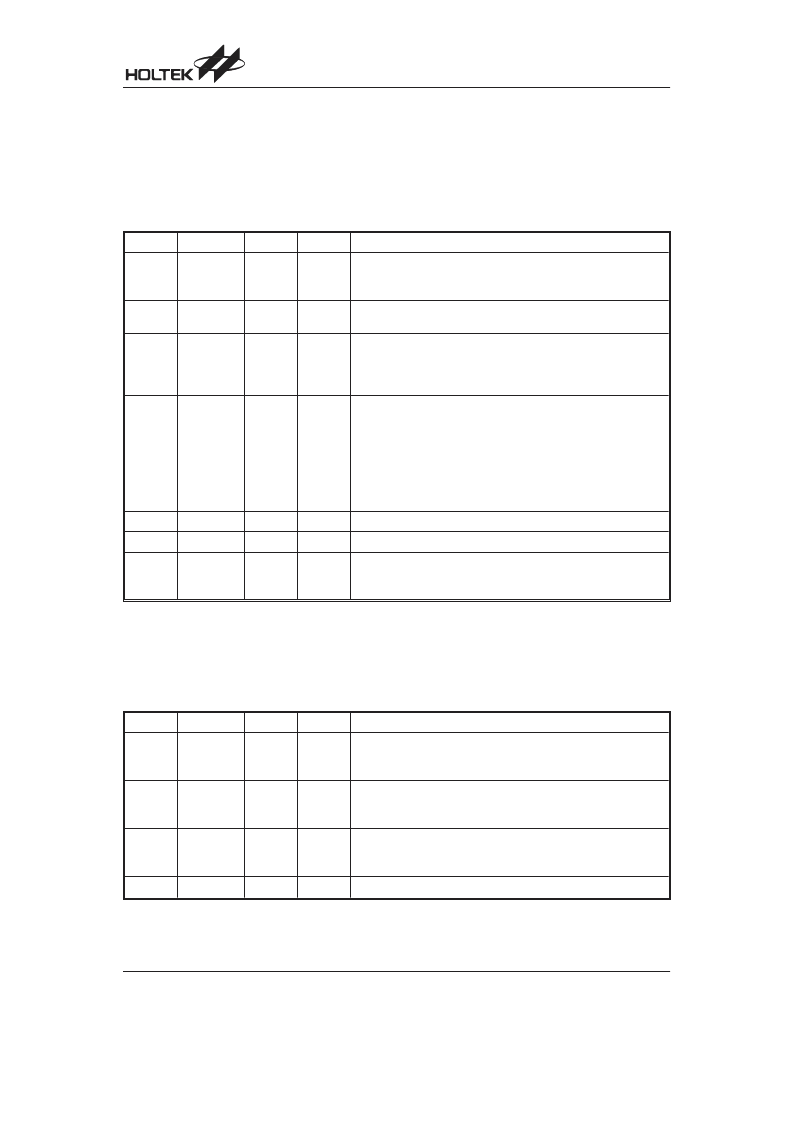

Bit No.

Label

R/W

Reset

Functions

0

SUSP

R

0

Read only, USB suspend indication. When this bit is set to 1 (set

by SIE), it indicates the USB bus enters suspend mode. The USB in-

terrupt is also triggered on changing from low to high of this bit.

1

RMWK

R/W

0

USB remote wake-up command. It is set by MCU to force the USB

host leaving the suspend mode.

2

URST

R/W

0

USB reset indication. This bit is set/cleared by USB SIE. This bit is

used to detect USB reset event on USB bus. When this bit is set to

1 ,thisindicatesanUSBresetisoccurredandanUSBinterruptwill

be initialized.

3

RESUME

R

0

USB resume indication. When the USB leaves suspend mode, this

bit is set to 1 (set by SIE). When the RESUME is set by SIE, an in-

terrupt will be generated to wake-up the MCU. In order to detecting

the suspend state, MCU should set USBCKEN and clear SUSP2 (in

UCC register) to enable the SIE detecting function. The RESUME

will be cleared while the SUSP is going 0 . When MCU is detecting

the SUSP, the RESUME (causes MCU to wake-up) should be re-

membered and token into consideration.

4

V33O

R/W

0

0/1: Turn-off/on V33O output

5~6

Undefined bit, read as 0 .

7

URD

R/W

1

USB reset signal control function definition

1: USB reset signal will reset MCU

0: USB reset signal cannot reset MCU

USC (20H) Register

The USR (USB endpoint interrupt status register) register is used to indicate which endpoint is accessed and to select

serialbus(USB).Theendpointrequestflags(EP0F,EP1F,EP2F)areusedtoindicatewhichendpointsareaccessed.If

an endpoint is accessed, the related endpoint request flag will be set to 1 and the USB interrupt will occur (if USB in-

terrupt is enabled and the stack is not full). When the active endpoint request flag is served, the endpoint request flag

has to be cleared to 0 by software.

Bit No.

Label

R/W

Reset

Functions

0

EP0F

R/W

0

When this bit is set to 1 (set by SIE). It indicates the endpoint 0 is

accessed and an USB interrupt will occur. When the interrupt has

been served, this bit should be cleared by software.

1

EP1F

R/W

0

When this bit is set to 1 (set by SIE). It indicates the endpoint 1 is

accessed and an USB interrupt will occur. When the interrupt has

been served, this bit should be cleared by software.

2

EP2F

R/W

0

When this bit is set to 1 (set by SIE). It indicates the endpoint 2 is

accessed and an USB interrupt will occur. When the interrupt has

been served, this bit should be cleared by software.

3~7

Undefined bit, read as 0 .

USR (21H) Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82A821R_07 | USB Audio MCU |

| HT82A822R | USB Audio MCU |

| HT82A822R_07 | USB Audio MCU |

| HT82A832R | Basic USB Phone OTP MCU |

| HT82A850R | Audio MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82A821R_07 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Audio MCU |

| HT82A822R | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Audio MCU |

| HT82A822R_07 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Audio MCU |

| HT82A824R | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Audio MCU |

| HT82A832R | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Audio MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。