- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385400 > HT48RA0A (Holtek Semiconductor Inc.) 8-Bit Remote Type MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT48RA0A |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit Remote Type MCU |

| 中文描述: | 8位遙控型單片機(jī) |

| 文件頁數(shù): | 9/31頁 |

| 文件大小: | 328K |

| 代理商: | HT48RA0A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

HT48RA0A

Rev. 1.70

9

July 16, 2003

Carrier

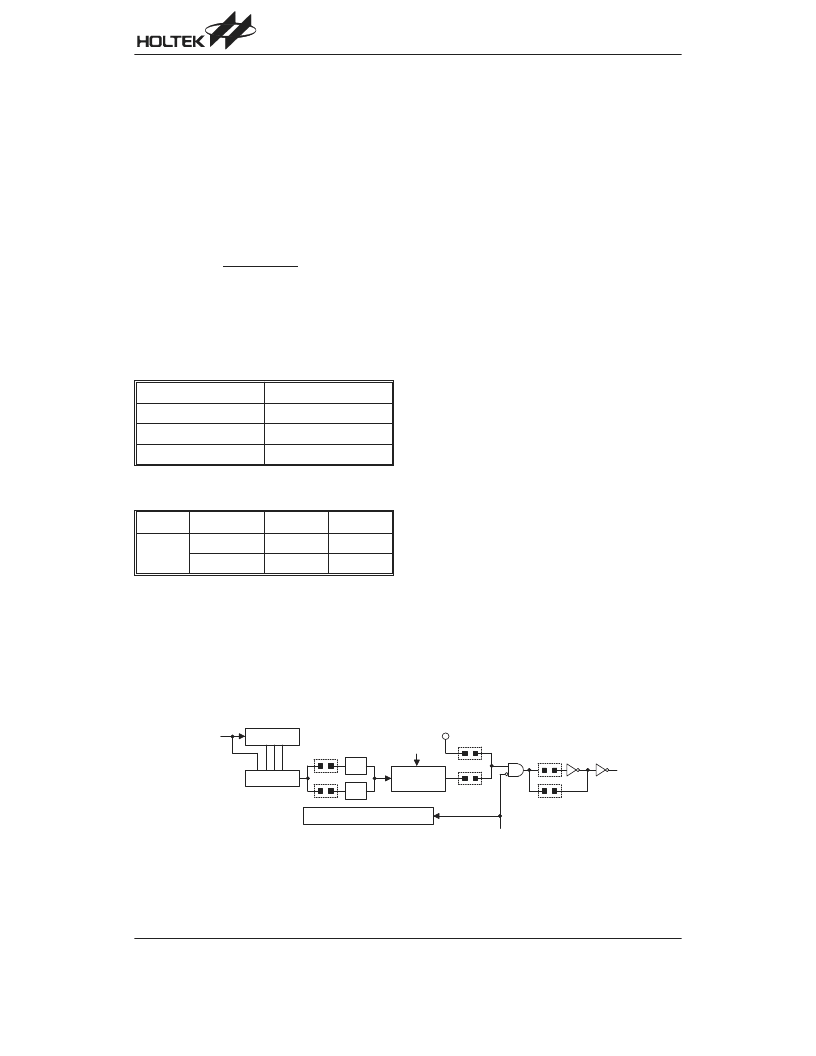

The HT48RA0A provides a carrier output which shares

the pin with PC0. It can be selected to be a carrier output

(REM) or level output pin (PC0) by code option. If the

carrier output option is selected, setting PC0= 0 to en-

able carrier output and setting PC0= 1 to disable it at

low level output.

The clock source of the carrier is implemented by in-

struction clock (system clock divided by 4) and pro-

cessed by a frequency divider to yield various carry

frequency.

Carry Frequency=

Clock Source

m 2

n

where m=2 or 3 and n=0~3, both are selected by code

option. If m=2, the duty cycle of the carrier output is 1/2

duty. If m=3, the duty cycle of the carrier output can be

1/2dutyor1/3dutyalsodeterminedbycodeoption(with

the exception of n=0).

Detailed selection of the carrier duty is shown below:

m 2

n

Duty Cycle

2, 4, 8, 16

1/2

3

1/3

6, 12, 24

1/2 or 1/3

The following table shows examples of carrier fre-

quency selection.

f

SYS

f

CARRIER

Duty

m 2

n

455kHz

37.92kHz

1/3 only

3

56.9kHz

1/2 only

2

Input/Output Ports

There are an 8-bit bidirectional input/output port, a 6-bit

input with 2-bit I/O port and one-bit output port in the

HT48RA0A,labeledPA,PBandPCwhicharemappedto

[12H], [14H], [16H] of the RAM, respectively. Each bit of

PA can be selected as NMOS output or Schmitt trigger

with pull-high resistor by software instruction. PB0~PB1

have the same structure with PA, while PB2~PB7 can

only be used for input operation (Schmitt trigger with

pull-high resistors). PC is only one-bit output port shares

the pin with carrier output. If the level option is selected,

the PC is CMOS output.

Both PA and PB for the input operation, these ports are

non-latched, that is, the inputs should be ready at the T2

rising edge of the instruction MOV A, [m] (m=12H or

14H). For PA, PB0~PB1 and PC output operation, all

data are latched and remain unchanged until the output

latch is rewritten.

When the PA and PB0~PB1 is used for input operation,

it should be noted that before reading data from pads, a

1 should be written to the related bits to disable the

NMOS device. That is, the instruction SET[m].i (i=0~7

for PA, i=0~1 for PB) is executed first to disable related

NMOSdevice,andthen MOVA,[m] togetstabledata.

After chip reset, PA and PB remain at a high level input

line while PC remain at high level output, if the level op-

tion is selected.

Each bit of PA, PB0~PB1 and PC output latches can be

set or cleared by the

(m=12H, 14H or 16H) instructions respectively.

SET [m].i

and

CLR [m].i

Some instructions first input data and then follow the

output operations. For example, SET [m].i , CLR [m] ,

CPL [m] , CPLA [m] read the entire port states into

theCPU,executethedefinedoperations(bit-operation),

and then write the results back to the latches or to the

accumulator.

Each line of PB has a wake-up capability to the device

by code option. The highest seven bits of PC are not

physically implemented, on reading them a 0 is re-

turned and writing results in a no-operation.

!

"

#

# $ %

#

%

&

'

(

# # "

)

" * +

'

(

#

#

,

#

#

,

Carrier/Level output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT48RA3 | 8-Bit Remote Type OTP MCU |

| HT48RB8 | 8-Bit USB Type OTP MCU |

| HT49C10 | 8-BIT MICROCONTROLLER |

| HT49C30L | HDSP-A101 RED DISPLAY, LED, |

| HT49R30 | DISPLAY 7 SEGMENT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT48RA0A(20SOP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|SOP|20PIN|PLASTIC |

| HT48RA0A(24SOP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|SOP|24PIN|PLASTIC |

| HT48RA0A-20SOP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| HT48RA0A-24SOP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| HT48RA1 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Remote Type 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。