- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46R64 (Holtek Semiconductor Inc.) A/D with LCD Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號: | HT46R64 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D with LCD Type 8-Bit MCU |

| 中文描述: | 在A / D液晶型8位微控制器 |

| 文件頁數(shù): | 19/47頁 |

| 文件大小: | 345K |

| 代理商: | HT46R64 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

HT46R64/HT46C64

Rev. 1.40

19

September 21, 2004

tions. Only one PFD (PFD0 or PFD1) can be applied to

PA3 by options. If PA3 is set as PFD output, there are

two types of selections; One is PFD0 as the PFD output,

the other is PFD1 as the PFD output. PFD0, PFD1 are

the timer overflow signals of the Timer/Event Counter 0,

Timer/Event Counter 1 respectively. No matter what the

operation mode is, writing a 0 to ET0I or ET1I disables

the related interrupt service. When the PFD function is

selected, executing SET [PA].3 instruction to enable

PFD output and executing CLR [PA].3 instruction to

disable PFD output.

In the case of timer/event counter OFF condition, writing

data to the timer/event counter preload register also re-

loads that data to the timer/event counter. But if the

timer/event counter is turn on, data written to the

timer/event counter is kept only in the timer/event coun-

ter preload register. The timer/event counter still contin-

ues its operation until an overflow occurs.

When the timer/event counter (reading TMR0/TMR1) is

read, the clock is blocked to avoid errors, as this may re-

sults in a counting error. Blocking of the clock should be

taken into account by the programmer. It is strongly rec-

ommended to load a desired value into the TMR0/TMR1

register first, before turning on the related timer/event

counter, for proper operation since the initial value of

TMR0/TMR1 is unknown. Due to the timer/event coun-

ter scheme, the programmer should pay special atten-

tion on the instruction to enable then disable the timer

for the first time, whenever there is a need to use the

timer/event counter function, to avoid unpredictable re-

sult. After this procedure, the timer/event function can

be operated normally.

The bit0~bit2 of the TMR0C can be used to define the

pre-scaling stages of the internal clock sources of

timer/eventcounter0.Thedefinitionsareasshown.The

overflow signal of timer/event counter can be used to

generate the PFD signal. The timer prescaler is also

used as the PWM counter.

Input/Output Ports

There are 24 bidirectional input/output lines in the

microcontroller, labeled as PA, PB and PD, which are

mapped to the data memory of [12H], [14H] and [18H]

respectively. All of these I/O ports can be used for input

and output operations. For input operation, these ports

are non-latching, that is, the inputs must be ready at the

T2 rising edge of instruction MOV A,[m] (m=12H, 14H

or 18H). For output operation, all the data is latched and

remains unchanged until the output latch is rewritten.

Each I/O line has its own control register (PAC, PBC,

PDC) to control the input/output configuration. With this

control register, CMOS output or Schmitt Trigger input

with or without pull-high resistor structures can be re-

configured dynamically under software control. To func-

tion as an input, the corresponding latch of the control

register must write 1 . The input source also depends

on the control register. If the control register bit is 1 ,

the input will read the pad state. If the control register bit

is 0 , the contents of the latches will move to the inter-

nal bus. The latter is possible in the read-modify-write

instruction.

For output function, CMOS is the only configuration.

These control registers are mapped to locations 13H,

15H and 19H.

Afterachipreset,theseinput/outputlinesremainathigh

levels or floating state (depending on pull-high options).

Each bit of these input/output latches can be set or

cleared by SET [m].i and CLR [m].i (m=12H, 14H or

18H) instructions.

Some instructions first input data and then follow the

output operations. For example,

SET [m].i ,

CLR

[m].i , CPL [m] , CPLA [m] read the entire port states

into the CPU, execute the defined operations

(bit-operation), and then write the results back to the

latches or the accumulator.

Each line of port A has the capability of waking-up the

device.

Each I/O port has a pull-high option. Once the pull-high

option is selected, the I/O port has a pull-high resistor,

otherwise, there s none. Take note that a non-pull-high

I/O port operating in input mode will cause a floating

state.

The PA3 is pin-shared with the PFD signal. If the PFD

option is selected, the output signal in output mode of

PA3 will be the PFD signal generated by timer/event

counter overflow signal. The input mode always retain

its original functions. Once the PFD option is selected,

the PFD output signal is controlled by PA3 data register

only. Writing 1 to PA3 data register will enable the PFD

output function and writing 0 will force the PA3 to remain

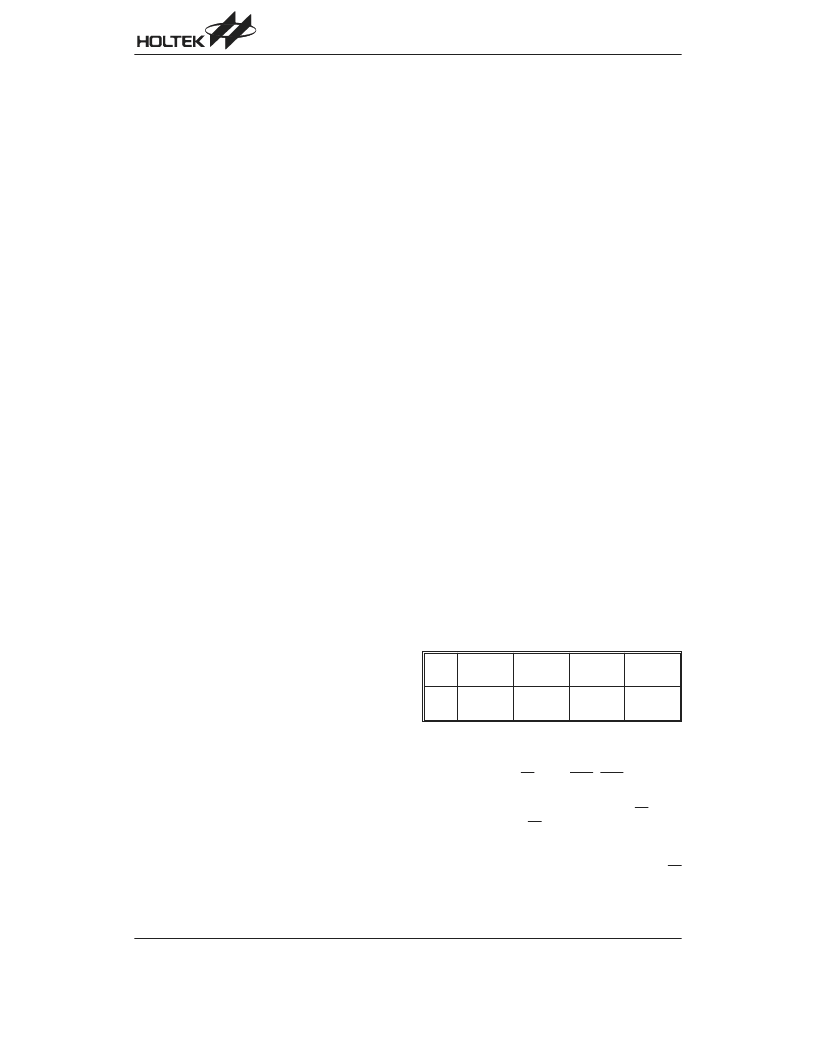

at 0 . The I/O functions of PA3 are shown below.

I/O

Mode

I/P

(Normal)

O/P

(Normal)

I/P

(PFD)

O/P

(PFD)

PA3

Logical

Input

Logical

Output

Logical

Input

PFD

(Timer on)

Note:

The PFD frequency is the timer/event counter

overflowfrequencydividedby2.

The PA0, PA1, PA3, PD4, PD5, PD6 and PD7 are

pin-shared with BZ, BZ, PFD, INT0, INT1, TMR0 and

TMR1 pins respectively.

The PA0 and PA1 are pin-shared with BZ and BZ signal,

respectively. If the BZ/BZ option is selected, the output

signal in output mode of PA0/PA1 will be the buzzer sig-

nal generated by multi-function timer. The input mode

always remain in its original function. Once the BZ/BZ

option is selected, the buzzer output signal are con-

trolled by the PA0, PA1 data register only.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46R23 | 8-Bit OTP Microcontroller |

| HT46R47 | 8-Bit OTP Battery Charger Controller |

| HT46R65-100 | A/D with LCD Type 8-Bit MCU |

| HT46C65 | A/D with LCD Type 8-Bit MCU |

| HT46C65-100 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46R64_06 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R64_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R65 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R65_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R65-100 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。