- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46R64 (Holtek Semiconductor Inc.) A/D with LCD Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT46R64 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D with LCD Type 8-Bit MCU |

| 中文描述: | 在A / D液晶型8位微控制器 |

| 文件頁(yè)數(shù): | 18/47頁(yè) |

| 文件大?。?/td> | 345K |

| 代理商: | HT46R64 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

HT46R64/HT46C64

Rev. 1.40

18

September 21, 2004

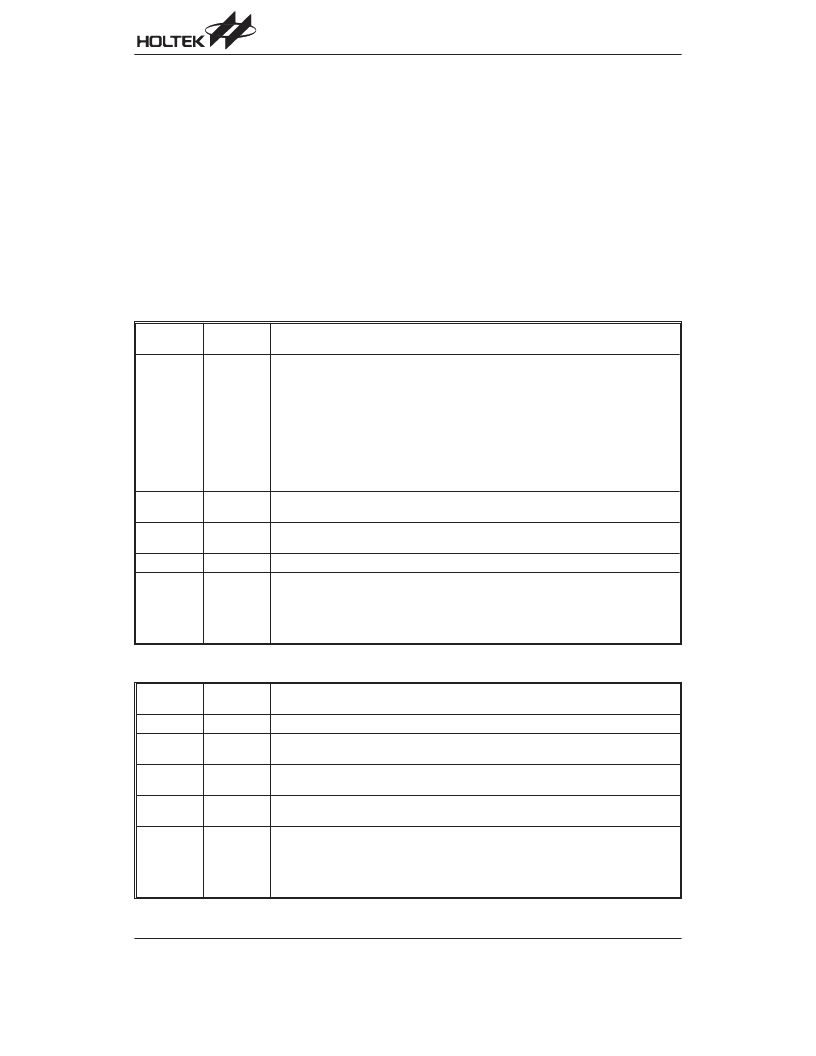

Label

(TMR1C)

Bits

Function

0~2

Unused bit, read as 0

T1E

3

Defines the TMR1 active edge of the timer/event counter

(0= active on low to high; 1= active on high to low)

T1ON

4

Enable/disable timer counting

(0= disabled; 1= enabled)

T1S

5

Defines the TMR1 internal clock source

(0=f

SYS

/4; 1=32768Hz)

T1M0

T1M1

6

7

Defines the operating mode T1M1, T1M0=

01= Event count mode (External clock)

10= Timer mode (Internal clock)

11= Pulse Width measurement mode (External clock)

00= Unused

TMR1C Register

In the event count or timer mode, the timer/event coun-

ter 0(1) starts counting at the current contents in the

timer/event counter 0(1) and ends at FFH(FFFFH).

Once an overflow occurs, the counter is reloaded from

the timer/event counter preload register, and generates

an interrupt request flag (T0F; bit 6 of INTC0, T1F; bit 4

of INTC1). In the pulse width measurement mode with

the values of the T0ON/T1ON and T0E/T1E bits equal

to 1, after the TMR0 (TMR1) has received a transient

from low to high (or high to low if the TE bit is 0 ), it will

start counting until the TMR0 (TMR1) returns to the orig-

inal level and resets the T0ON/T1ON. The measured re-

sult remains in the timer/event counter even if the

activated transient occurs again. In other words, only

1-cycle measurement can be made until the

T0ON/T1ON is set. The cycle measurement will

re-function as long as it receives further transient pulse.

In this operation mode, the timer/event counter begins

counting not according to the logic level but to the tran-

sient edges. In the case of counter overflows, the coun-

ter is reloaded from the timer/event counter register and

issues an interrupt request, as in the other two modes,

i.e., event and timer modes.

To enable the counting operation, the Timer ON bit

(T0ON: bit 4 of TMR0C; T1ON: bit 4 of TMR1C) should

be set to 1. In the pulse width measurement mode, the

T0ON/T1ON is automatically cleared after the measure-

ment cycle is completed. But in the other two modes, the

T0ON/T1ON can only be reset by instructions. The

overflow of the Timer/Event Counter 0/1 is one of the

wake-upsourcesandcanalsobeappliedtoaPFD(Pro-

grammable Frequency Divider) output at PA3 by op-

Label

(TMR0C)

Bits

Function

T0PSC0

T0PSC1

T0PSC2

0

1

2

To define the prescaler stages.

T0PSC2, T0PSC1, T0PSC0=

000: f

INT

=f

SYS

001: f

INT

=f

SYS

/2

010: f

INT

=f

SYS

/4

011: f

INT

=f

SYS

/8

100: f

INT

=f

SYS

/16

101: f

INT

=f

SYS

/32

110: f

INT

=f

SYS

/64

111: f

INT

=f

SYS

/128

T0E

3

Defines the TMR active edge of timer/event counter

(0=active on low to high; 1=active on high to low)

T0ON

4

Enable/disable timer counting

(0=disabled; 1=enabled)

5

Unused bit, read as 0

T0M0

T0M1

6

7

Defines the operating mode T0M1, T0M0=

01= Event count mode (External clock)

10= Timer mode (Internal clock)

11= Pulse Width measurement mode (External clock)

00= Unused

TMR0C Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46R23 | 8-Bit OTP Microcontroller |

| HT46R47 | 8-Bit OTP Battery Charger Controller |

| HT46R65-100 | A/D with LCD Type 8-Bit MCU |

| HT46C65 | A/D with LCD Type 8-Bit MCU |

| HT46C65-100 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46R64_06 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R64_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R65 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R65_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R65-100 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。