- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385399 > HT46C62 (Holtek Semiconductor Inc.) A/D with LCD Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT46C62 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D with LCD Type 8-Bit MCU |

| 中文描述: | 在A / D液晶型8位微控制器 |

| 文件頁(yè)數(shù): | 13/46頁(yè) |

| 文件大小: | 401K |

| 代理商: | HT46C62 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

HT46R62/HT46C62

Rev. 1.60

13

July 14, 2005

The RTC oscillator circuit can be controlled to oscillate

quickly by setting the QOSC bit (bit 4 of RTCC). It is

recommended to turn on the quick oscillating function

upon power on, and then turn it off after 2 seconds.

The WDT oscillator is a free running on-chip RC oscilla-

tor, and no external components are required. Although

the system enters the power down mode, the system

clock stops, and the WDT oscillator still works with a pe-

riod of approximately 65 s@5V. The WDToscillator can

be disabled by options to conserve power.

Watchdog Timer

WDT

The WDT clock source is implemented by a dedicated

RC oscillator (WDT oscillator) or an instruction clock

(system clock/4) or a real time clock oscillator (RTC os-

cillator). The timer is designed to prevent a software

malfunction or sequence from jumping to an unknown

location with unpredictable results. The WDT can be

disabled by options. But if the WDT is disabled, all exe-

cutions related to the WDT lead to no operation.

Once an internal WDT oscillator (RC oscillator with pe-

riod 65 s@5V normally) is selected, it is divided by

2

12

~2

15

(by option to get the WDT time-out period). The

minimum period of WDT time-out period is about

300ms~600ms. This time-out period may vary with tem-

perature, VDD and process variations. By selection the

WDT option, longer time-out periods can be realized. If

theWDTtime-outisselected2

15

,themaximumtime-out

period is divided by 2

15

~2

16

about 2.1s~4.3s. If the WDT

oscillator is disabled, the WDTclock may still come from

the instruction clock and operate in the same manner

except that in the halt state the WDT may stop counting

and lose its protecting purpose. In this situation the logic

can only be restarted by external logic. If the device op-

erates in a noisy environment, using the on-chip RC os-

cillator (WDT OSC) is strongly recommended, since the

HALT will stop the system clock.

The WDT overflow under normal operation initializes a

chip reset and sets the status bit TO . In the HALT

mode, the overflow initializes a warm reset , and only

the program counter and SP are reset to zero. To clear

the contents of the WDT, there are three methods to be

adopted, i.e., external reset (a low level to RES), soft-

ware instruction, and a HALT instruction. There are

two types of software instructions; CLR WDT and the

other set

two types of instruction, only one type of instruction can

CLR WDT1 and CLR WDT2 . Of these

be active at a time depending on the options

CLR

WDT times selection option. If the CLR WDT is se-

lected (i.e., CLR WDT times equal one), any execution

of the CLR WDT instruction clears the WDT. In the

case that CLR WDT1 and CLR WDT2 are chosen

(i.e., CLR WDT times equal two), these two instructions

have to be executed to clear the WDT; otherwise, the

WDT may reset the chip due to time-out.

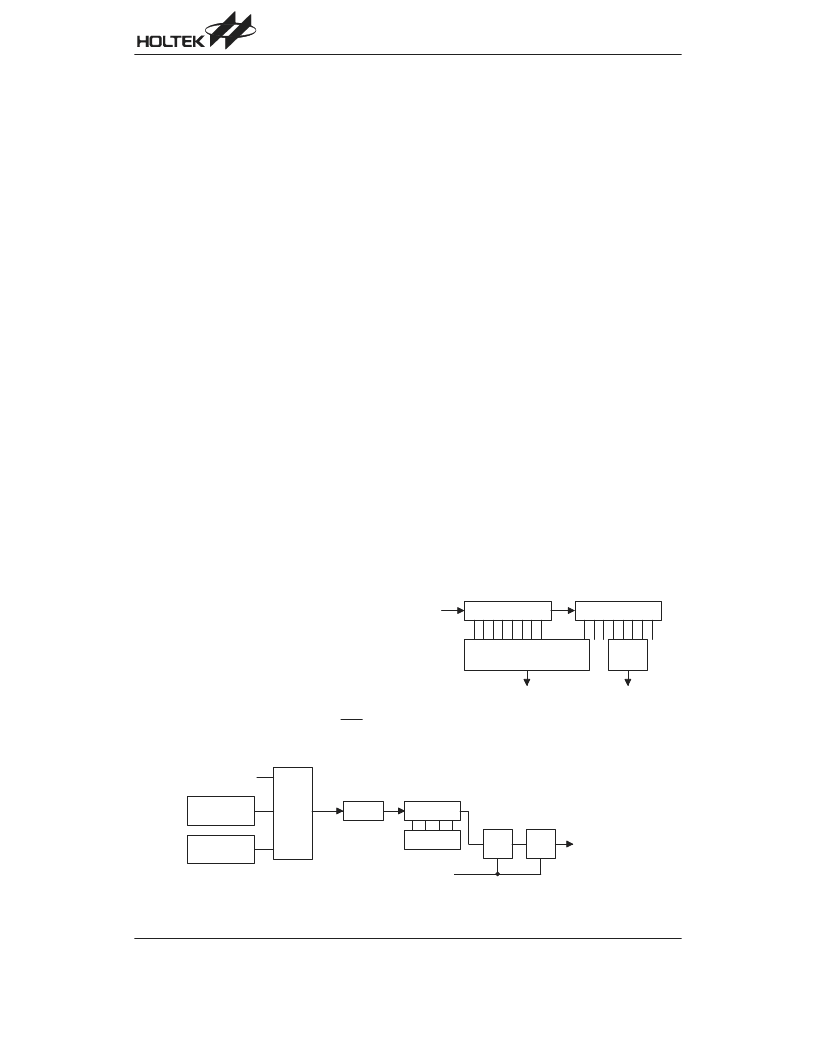

Multi-function Timer

The HT46R62/HT46C62 provides a multi-function timer

for the WDT, time base and RTC but with different

time-out periods. The multi-function timer consists of an

8-stage divider and a 7-bit prescaler, with the clock

source coming from the WDT OSC or RTC OSC or the

instruction clock (i.e., system clock divided by 4). The

multi-function timer also provides a selectable fre-

quency signal (ranges from f

S

/2

2

to f

S

/2

8

) for LCD driver

circuits, and a selectable frequency signal (ranging from

f

S

/2

2

to f

S

/2

9

) for the buzzer output by options. It is rec-

ommended to select a nearly 4kHz signal for the LCD

driver circuits to have proper display.

Time Base

The time base offers a periodic time-out period to gener-

ate a regular internal interrupt. Its time-out period

ranges from 2

12

/f

S

to 2

15

f

S

selected by options. If time

base time-out occurs, the related interrupt request flag

(TBF; bit 5 of INTC1) is set. But if the interrupt is en-

abled, and the stack is not full, a subroutine call to loca-

tion 14H occurs.

#

(

2

> -

8

'

(

2

2

'

> 9

6 3 / 9

)

)

&

7

(

4

- & ,

3

- &

- & ,

4

- &

- & ,

- &

- & ,

- &

'

2

& -

/

Watchdog Timer

( ( ( ( ( ( ( (

&

8

2

$

(

8

( : & -

, & -

/

;

*

( : & -

, & -

.

;

( *

(

- & ,

4

- &

Time Base

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46R62 | A/D with LCD Type 8-Bit MCU |

| HT46C63 | A/D with LCD Type 8-Bit MCU |

| HT46C63-100QEP-A | A/D with LCD Type 8-Bit MCU |

| HT46C63-56SSOP-A | A/D with LCD Type 8-Bit MCU |

| HT46R63 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46C63 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46C63(100QFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| HT46C63-100QEP-A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46C63-56SSOP-A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46C64 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。