- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385396 > HSP9520 (Intersil Corporation) Multilevel Pipeline Registers PDF資料下載

參數(shù)資料

| 型號(hào): | HSP9520 |

| 廠商: | Intersil Corporation |

| 英文描述: | Multilevel Pipeline Registers |

| 中文描述: | 多級(jí)流水線寄存器 |

| 文件頁(yè)數(shù): | 1/4頁(yè) |

| 文件大?。?/td> | 25K |

| 代理商: | HSP9520 |

1

File Number

2811.5

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright Intersil Corporation 1999

HSP9520, HSP9521

Multilevel Pipeline Registers

These devices are multilevel pipeline registers implemented

using a low power CMOS process. They are pin for pin

compatible replacements for industry standard multilevel

pipeline registers such as the L29C520 and L29C521. The

HSP9520 and HSP5921 are direct replacements for the

AM29520 and AM29521 and WS59520 and WS59521.

They consist of four 8-bit registers which are dual ported.

They can be configured as a single four level pipeline or a

dual two level pipeline. A single 8-bit input is provided, and

the pipelining configuration is determined by the instruction

code input to the I0 and I1 inputs (see instruction control).

The contents of any of the four registers is selectable at the

multiplexed outputs through the use of the S0 and S1

multiplexer control inputs (see register select. The output is 8

bits wide and is three-stated through the use of the OE input.

The HSP9520 and HSP9521 differ only in the way data is

loaded into and between the registers in dual two-level

operation. In the HSP9520 when data is loaded into the first

level the existing data in the first level is moved to the second

level. In the HSP9521 loading the first level simply causes

the current data to be overwritten. Transfer of data to the

second level is achieved using the single four level mode (I1,

I0 = ‘0’). This instruction also causes the first level to be

loaded. The HOLD instruction (I1, I0 = ‘1’) provides a means

of holding the contents of all registers.

Features

Four 8-Bit Registers

Hold, Transfer and Load Instructions

Single 4-Stage or Dual-2 Stage Pipelining

All Register Contents Available at Output

Fully TTL Compatible

Three-State Outputs

High Speed, Low Power CMOS

Applications

Array Processor

Digital Signal Processor

A/D Buffer

Telecommunication

Byte Wide Shift Register

Mainframe Computers

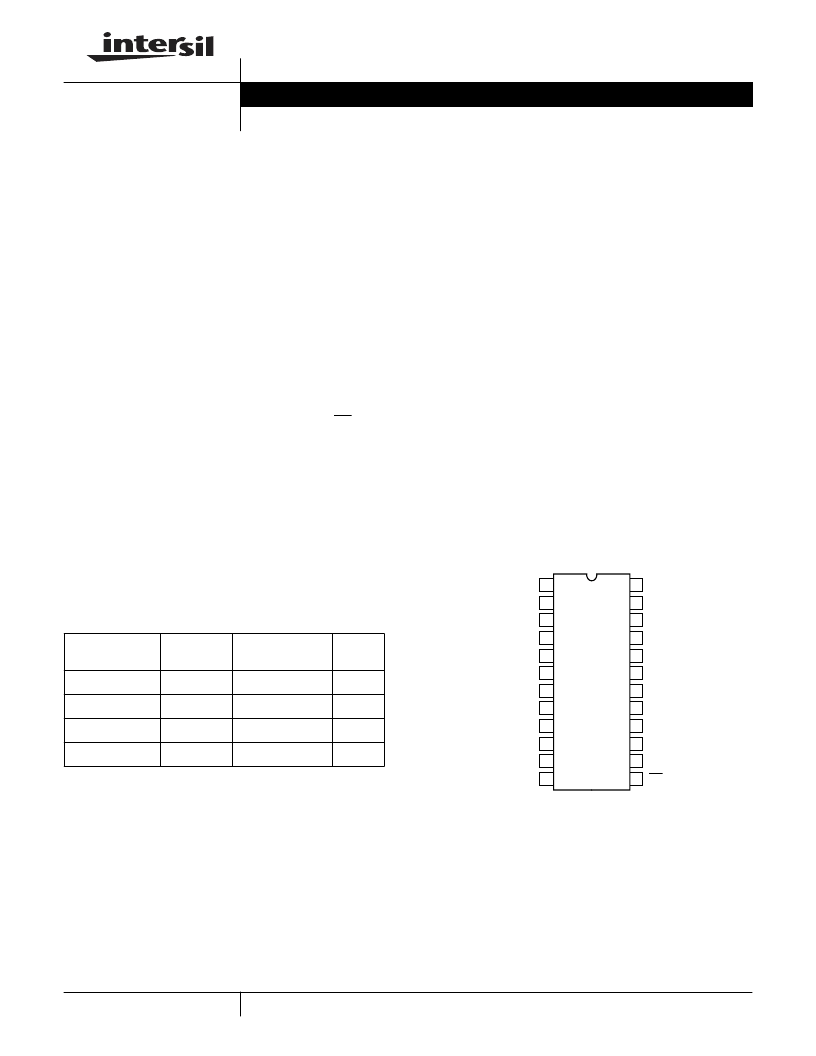

Pinout

HSP9520, HSP9521 (SOIC, PDIP)

TOP VIEW

Ordering Information

PART NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG.

NO.

HSP9520CP

0 to 70

24 Ld PDIP

E24.3

HSP9520CS

0 to 70

24 Ld SOIC

M24.3

HSP9521CP

0 to 70

24 Ld PDIP

E24.3

HSP9521CS

0 to 70

24 Ld SOIC

M24.3

I0

I1

D0

D1

D2

D3

D4

D5

D6

D7

CLK

GND

V

CC

S0

S1

Y0

Y1

Y2

Y4

Y6

Y7

Y3

Y5

OE

1

2

3

4

5

6

7

8

9

10

11

12

16

17

18

19

20

21

22

23

24

15

14

13

Data Sheet

May 1999

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP9520CP | Multilevel Pipeline Registers |

| HSP9520CS | Multilevel Pipeline Registers |

| HSP9521 | Multilevel Pipeline Registers |

| HSP9521CP | Multilevel Pipeline Registers |

| HSP9521CS | Multilevel Pipeline Registers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP9520 WAF | 制造商:Harris Corporation 功能描述: |

| HSP9520CP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP9520CS | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP9521 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Multilevel Pipeline Registers |

| HSP9521CP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。