- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385388 > HMS81008E (Hynix Semiconductor Inc.) HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | HMS81008E |

| 廠商: | Hynix Semiconductor Inc. |

| 元件分類: | 8位微控制器 |

| 英文描述: | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | Hynix半導(dǎo)體公司的8位單芯片微控制器 |

| 文件頁數(shù): | 39/77頁 |

| 文件大?。?/td> | 1112K |

| 代理商: | HMS81008E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

HMS81004E/08E/16E/24E/32E

36

JUNE 2001 Ver 1.00

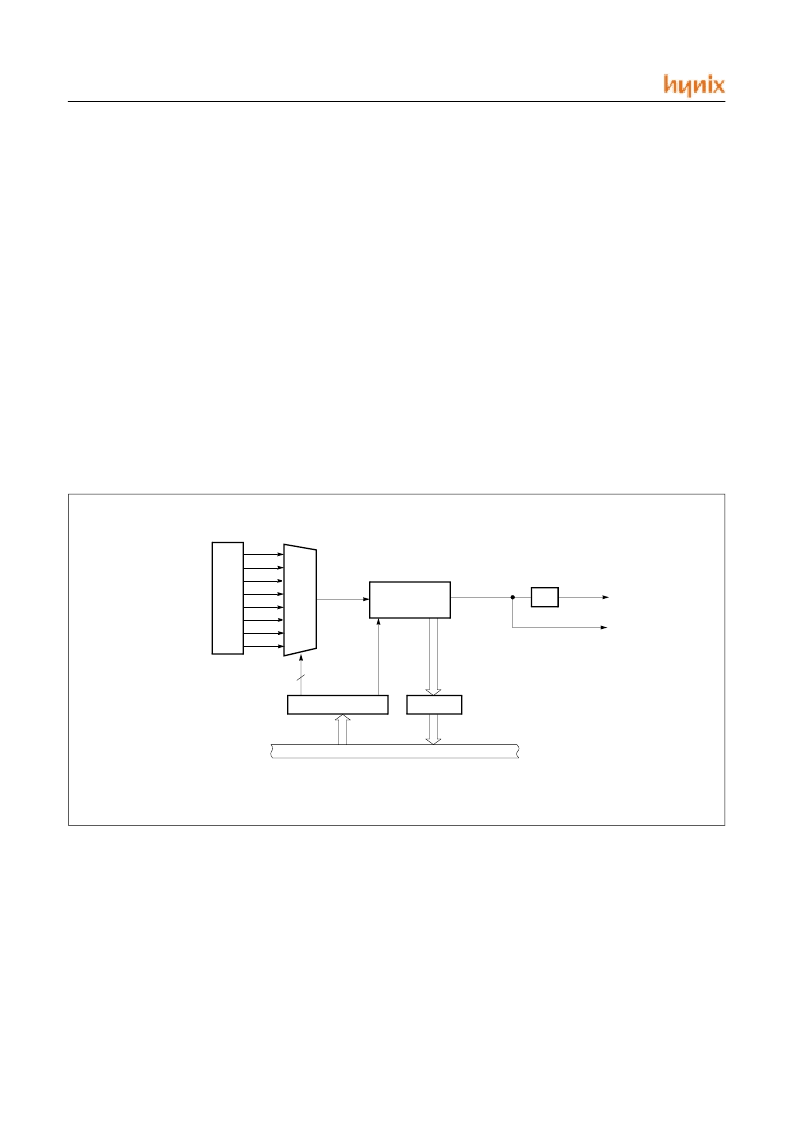

11. BASIC INTERVAL TIMER

The HMS81004E/08E/16E/24E/32E has one 8-bit Basic

Interval Timer that is free-run and can not stop. Block dia-

gram is shown in Figure 11-1 .

The Basic Interval Timer generates the time base for

Standby release time, watchdog timer counting, and etc. It

also provides a Basic interval timer interrupt (IFBIT). As

the count overflow from FF

H

to 00

H

, this overflow causes

the interrupt to be generated.

-8bit binary up-counter

-Use the bit output of prescaler as input to secure the oscil-

lation stabilization time after power-on

-Secures the oscillation stabilization time in standby mode

(stop mode) release

-Contents of B.I.T can be read

-Provides the clock for watch dog timer

The Basic Interval Timer is controlled by the clock control

register (CKCTLR) shown in Figure 11-2 . If bit3(BTCL)

of CKCTLR is set to “1”, B.I.T is cleared, and then, after

one machine cycle, BTCL becomes “0”, and B.I.T starts

counting. BTCL is set to ``0`` in reset state.

The input clock of B.I.T can be selected from the prescaler

within a range of 2us to 256us by clock input selection bits

(BTS2~BTS0). (at fex = 4MHz). In reset state, or power

on reset, BTS2=“1”, BTS1= “1”, BTS0= “1” to secure the

longest oscillation stabilization time. B.I.T can generate

the wide range of basic interval time interrupt request (IF-

BIT) by selecting prescaler output.

By reading of the Basic Interval Timer Register (BITR),

we can read counter value of B.I.T. Because B.I.T can be

cleared or read, the spending time up to maximum 65.5ms

can be available. B.I.T is read-only register. If B.I.T reg-

ister is written, then CKCTLR register with same address

is written.

Figure 11-1 Block diagram of Basic Interval Timer

MUX

Basic Interval Timer Interrupt

Select Input clock 3

Basic Interval Timer

source

clock

8-bit up-counter

BTS[2:0]

BTCL

÷

8

÷

16

÷

1024

÷

512

÷

256

÷

128

÷

64

÷

32

To Watchdog timer (WDTR)

CKCTLR

clear

overflow

Internal bus line

clock control register

[0C7

H

]

IFBIT

Read

P

BITR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMS81016E | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81024E | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81032E | HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81C43XX | CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER FOR TELEVISION |

| HMS87C1304A | CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMS81016 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REMOTE CONTROLLER |

| HMS81016E | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81020ET | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REMOTE CONTROLLER |

| HMS81020TL | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81024 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REMOTE CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。