- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370643 > HMS30C7080 (Electronic Theatre Controls, Inc.) Mobile Phone Camera Back-End Processor PDF資料下載

參數(shù)資料

| 型號: | HMS30C7080 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Mobile Phone Camera Back-End Processor |

| 中文描述: | 手機相機后端處理器 |

| 文件頁數(shù): | 70/161頁 |

| 文件大?。?/td> | 973K |

| 代理商: | HMS30C7080 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當(dāng)前第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁

HMS30C7110

2003 MagnaChip Semiconductor Ltd. All Rights Reserved

Version 1.5

70

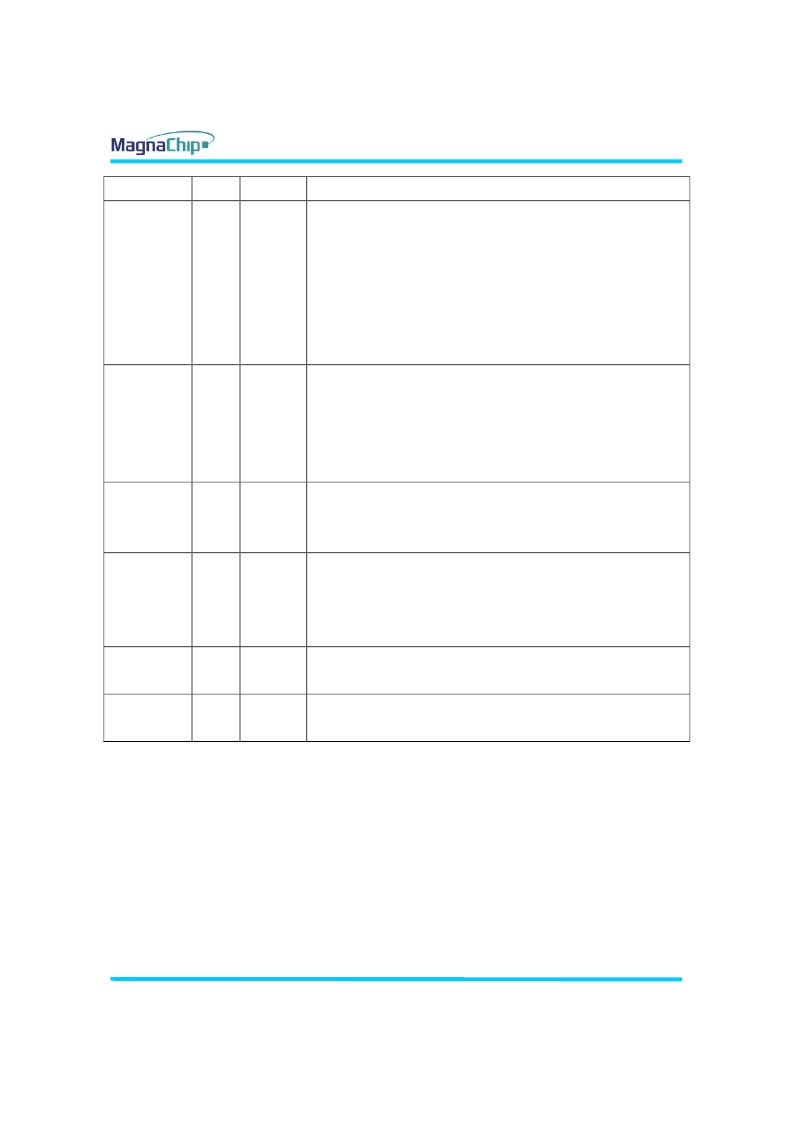

prior to the first MRXCLK that follows the final nibble.

MRXD[3:0]

4

I

Receive Data Nibble. Signals are the receive data nibble. They

are synchronized to the rising edge of MRXCLK. When

MRXDV is asserted, the PHY sends a data nibble to the RX

MAC. For a correctly interpreted frame, seven bytes of a

preamble and a completely formed SFD must be passed across

the interface. If 7-wire interface is selected, MRXD[0] will carry

data bits, all others will be unused.

MRXERR

1

I

Receive Error. PHY asserts this signal to indicate to the RX

MAC that a media error was detected during the transmission of

the current frame. MRXERR is synchronous to the MRXCLK

and is asserted for one or more MRXCLK clock periods and

then deasserted.

MCOLL

1

I

Collision Detected. The PHY asynchronously asserts the

collision signal MCOLL after the collision is detected on the

media. When deasserted, no collision is detected on the media.

MCRS

1

I

Carrier Sense. The PHY asynchronously asserts the carrier sense

MCRS signal after the medium is detected in a non-idle state.

When deasserted, signal indicates that the media is in the idle

state (and the transmission can start).

MDC

1

I

Management Data Clock. Clock for the MDIO serial data

channel.

MDIO

1

I/O

Management Data Input/Output. Bi-directional serial data

channel for PHY/STA communication.

PHY Interface Signals

2.6.2.

User Accessible Registers (Base = 0x1920_0000)

This section describes registers inside the Ethernet MAC. The address field in the following table

indicates an address offset in hexadecimal from Ethernet Base Address defined in the CPU section.

Width specifies the number of bits in the register and access specifies the valid access types of the

register. Where ‘RW’ stands for read and write access, ‘RO’ for read only access. A ‘C’ indicates

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMS30C7202 | 32-bit ARM7TDMI RISC static CMOS CPU core |

| HMS30C7202N | Highly-intergrated MPU |

| HMS81C2012A | CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

| HMS81C2012AK | CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

| HMS81C2012ALQ | CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMS30C7110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Multipurpose Network Processor |

| HMS30C7202 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:32-bit ARM7TDMI RISC static CMOS CPU core |

| HMS30C7202N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Highly-intergrated MPU |

| HMS30C7210 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ARM Based 32-Bit Microprocessor |

| HMS3224M3 | 制造商:HANBIT 制造商全稱:Hanbit Electronics Co.,Ltd 功能描述:SRAM MODULE 768KBit (32K x 24-Bit) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。