- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1646A Gigabit Ethernet Serialize/Deserialize (SerDes) IC(千兆位以太網(wǎng)串行器/解串行器) PDF資料下載

參數(shù)資料

| 型號: | HDMP-1646A |

| 英文描述: | Gigabit Ethernet Serialize/Deserialize (SerDes) IC(千兆位以太網(wǎng)串行器/解串行器) |

| 中文描述: | 千兆以太網(wǎng)序列化/反序列化器(SerDes)集成電路(千兆位以太網(wǎng)串行器/解串行器) |

| 文件頁數(shù): | 13/16頁 |

| 文件大?。?/td> | 248K |

| 代理商: | HDMP-1646A |

13

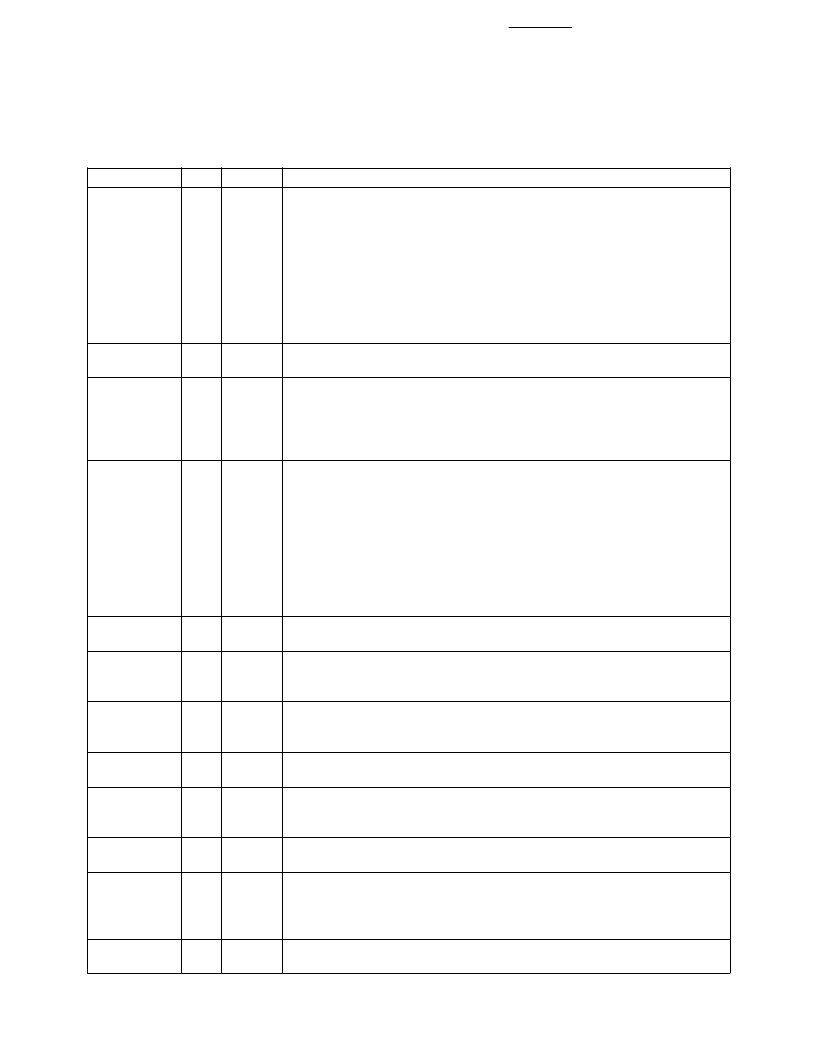

TRx I/O Definition (cont’d.)

Name

Pin

RX[0]

RX[1]

RX[2]

RX[3]

RX[4]

RX[5]

RX[6]

RX[7]

RX[8]

RX[9]

RXCAP0

RXCAP1

SIG_DET

Type

O-TTL

Signal

45

44

43

41

40

39

38

36

35

34

48

49

26

Data Outputs:

One 10 bit data byte. RX[0] is the first bit received.

RX[0] is the least significant bit. When there is a loss of input signal at

±

DIN, these outputs are held static at logic 1. Refer to SIG_DET (pin 26)

pin definition for more details.

C

Loop Filter Capacitor:

A loop filter capacitor for the internal PLL must

be connected across the RXCAP0 and RXCAP1 pins. (typical value = 0.1

μ

F).

Signal Detect:

Indicates a loss of signal on the high-speed differential inputs,

±

DIN, as in the case where the transmission cable becomes disconnected.

If

±

DIN >= 200 mV peak-to-peak, SIG_DET = logic 1.

If

±

DIN < 200 mV and

±

DIN > 50 mV, SIG_DET = undefined.

If

±

DIN <= 50 mV, SIG_DET = logic 0. RX[0:9] = 1111111111.

Data Inputs:

One 10 bit, 8B/10B-encoded data byte. TX[0] is the first

bit transmitted. TX[0] is the least significant bit.

O-TTL

TX[0]

TX[1]

TX[2]

TX[3]

TX[4]

TX[5]

TX[6]

TX[7]

TX[8]

TX[9]

TXCAP1

TXCAP0

V

CC

2

3

4

6

7

8

9

11

12

13

16

17

23

I-TTL

C

Loop Filter Capacitor:

A loop filter capacitor must be connected across

the TXCAP1 and TXCAP0 pins (typical value = 0.1

μ

F).

Logic Power Supply:

Normally 3.3 volts. Used for internal TX and RX

PECL logic. It should be isolated from the noisy TTL supply as well as

possible.

This pin is bonded to an isolated pad and has no functionality. However,

it is recommended that this pin be connected to V

CC

in order to conform

with the X3T11 “10-bit specification,” and to help dissipate heat.

Analog Power Supply:

Normally 3.3 volts. Used to provide a clean

supply line for the PLL and high-speed analog cells.

TTL Power Supply:

Normally 3.3 volts. Used for all TTL receiver output

buffer cells.

S

20,28

57,59

5

10,53

55

50

*V

CC

V

CC

_RXA

S

V

CC

_RXTTL

29

37

42

18

S

V

CC

_TXA

S

Analog Power Supply:

Normally 3.3 volts. Used to provide a clean

supply line for the PLL and high-speed analog cells.

High-Speed ECL Supply:

Normally 3.3 volts. Used only for the last stage

of the high-speed transmitter output cell (HS_OUT) as shown in

Figure 10. Due to high current transitions, this V

CC

should be well

bypassed to a ground plane.

High-Speed Supply:

Normally 3.3 volts. Used by the transmitter side for the

high-speed circuitry. Noise on this line should be minimized for best operation.

V

CC

_TXECL

60

S

V

CC

_TXHS

63

S

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1636A | Gigabit Ethernet Serialize/Deserialize (SerDes) IC(千兆位以太網(wǎng)串行器/解串行器) |

| HDMP-T1636A | Gigabit Ethernet Serialize/Deserialize (SerDes) IC(千兆位以太網(wǎng)串行器/解串行器) |

| HDN1075O | Plug-In Relay; Contacts:DPDT; Coil Voltage AC Max:120V; Contact Carry Current:10A; Relay Terminals:8-Pin Octal; Relay Mounting:Plug-In; Contact Carrying Power:2VA; Contact Rating:10A; Mounting Type:Plug In; Switch Function:DPDT |

| HDN1077O | Pressure Transducer, Series 19 mm, Compensated, Pressure Range: 0 psi to 200 psi, Gage, 1/4 BSPP, 10 Vdc excitation |

| HDN1075 | 0.28(7MM) SEVEN SEGMANT NUMERIC DISPLAY SOW CURRENT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP1646AG | 制造商:Agilent Technologies 功能描述: |

| HDMP-1685A | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Agilent HDMP-1685A 1.25 Gbps Four Channel SerDes with 5-pin DDR SSTL_2 Parallel Interface |

| HDMP-1687 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Four Channel SerDes Circuit for Gigabit Ethernet and Fibre Channel |

| HDMP-19-01-S-EM | 制造商:Samtec Inc 功能描述:HDMP INSULATOR FOR LOCKING PLUG - Bulk |

| HDMP2003 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FIBER OPTIC SUPPORT CIRCUIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。