- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384350 > GS8322Z18B-V (GSI TECHNOLOGY) 36Mb Pipelined and Flow Through Synchronous NBT SRAM PDF資料下載

參數(shù)資料

| 型號: | GS8322Z18B-V |

| 廠商: | GSI TECHNOLOGY |

| 英文描述: | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| 中文描述: | 流水線和流量分配36MB通過同步唑的SRAM |

| 文件頁數(shù): | 17/39頁 |

| 文件大?。?/td> | 973K |

| 代理商: | GS8322Z18B-V |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

Note:

The burst counter wraps to initial state on the 5th clock.

Note:

The burst counter wraps to initial state on the 5th clock.

Linear Burst Sequence

A[1:0] A[1:0] A[1:0] A[1:0]

1st address

00

01

10

11

2nd address

01

10

11

00

3rd address

10

11

00

01

4th address

11

00

01

10

Interleaved Burst Sequence

A[1:0] A[1:0] A[1:0] A[1:0]

1st address

00

01

10

11

2nd address

01

00

11

10

3rd address

10

11

00

01

4th address

11

10

01

00

GS8322Z18/36/72(B/E/C)-xxxV

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.05 6/2006

17/39

2002, GSI Technology

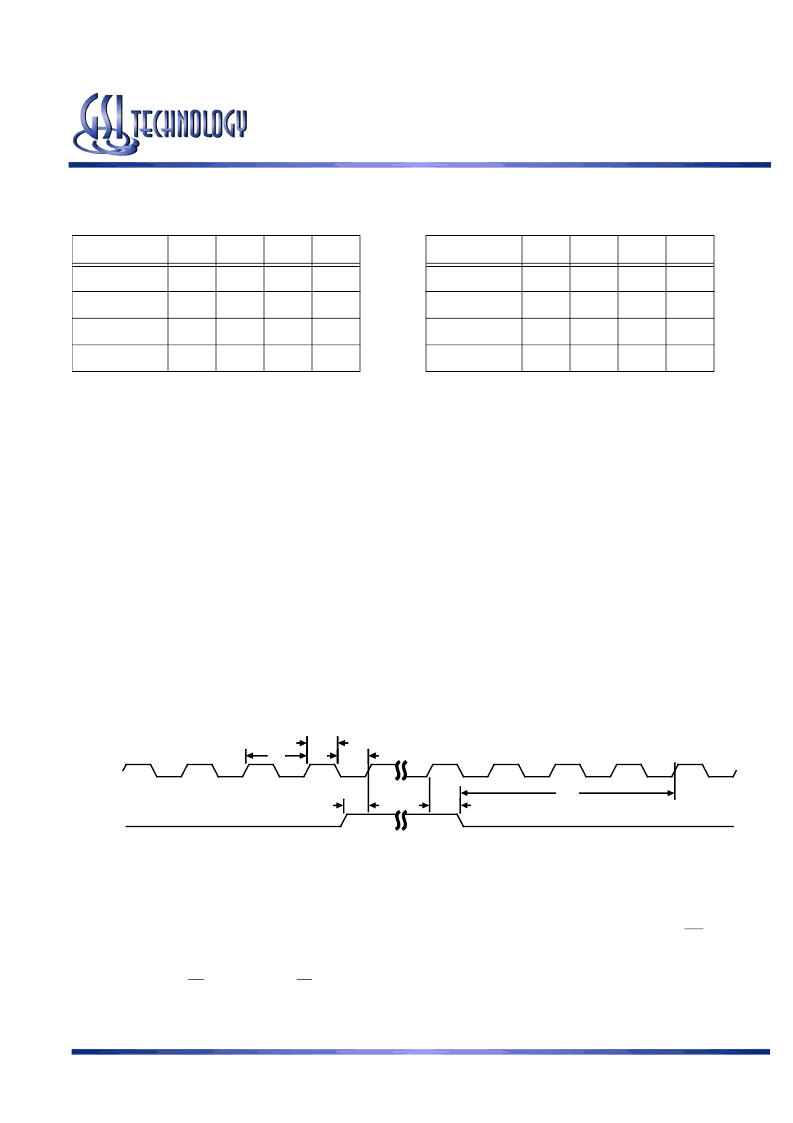

Burst Counter Sequences

BPR 1999.05.18

Sleep Mode

During normal operation, ZZ must be pulled low, either by the user or by its internal pull down resistor. When ZZ is pulled high,

the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to

low, the SRAM operates normally after 2 cycles of wake up time.

Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to I

SB

2. The duration of

Sleep mode is dictated by the length of time the ZZ is in a High state. After entering Sleep mode, all inputs except ZZ become

disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode.

When the ZZ pin is driven high, I

SB

2 is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending

operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated

until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a Deselect or Read commands

may be applied while the SRAM is recovering from Sleep mode.

Sleep Mode Timing Diagram

tZZR

tZZH

tZZS

tKL

tKH

tKC

CK

ZZ

Designing for Compatibility

The GSI NBT SRAMs offer users a configurable selection between Flow Through mode and Pipeline mode via the FT signal. Not

all vendors offer this option, however most mark the pin V

DD

or V

DDQ

on pipelined parts and V

SS

on flow through parts. GSI NBT

SRAMs are fully compatible with these sockets. Other vendors mark the pin as a No Connect (NC). GSI RAMs have an internal

pull-up device on the FT pin so a floating FT pin will result in pipelined operation. If the part being replaced is a pipelined mode

part, the GSI RAM is fully compatible with these sockets. In the unlikely event the part being replaced is a Flow Through device,

the pin will need to be pulled low for correct operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS8322Z18E-133IV | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8322Z18E-133V | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8322Z18E-150IV | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8322Z18E-150V | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8322Z18E-166IV | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS8322Z18E-133 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 36MBIT 2MX18 8.5NS/4NS 165FBGA - Trays |

| GS8322Z18E-133I | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 36MBIT 2MX18 8.5NS/4NS 165FBGA - Trays |

| GS8322Z18E-133IV | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V/2.5V 36MBIT 2MX18 8.5NS/4NS 165FPBGA - Trays |

| GS8322Z18E-133V | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V/2.5V 36MBIT 2MX18 8.5NS/4NS 165FPBGA - Trays |

| GS8322Z18E-150 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 36MBIT 2MX18 8.5NS/3.8NS 165FBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。