- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4316 > EP1S80F1508C6N (Altera)IC STRATIX FPGA 80K LE 1508-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EP1S80F1508C6N |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 510/864頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC STRATIX FPGA 80K LE 1508-FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 產(chǎn)品變化通告: | Package Height Change 03/March/2008 |

| 標(biāo)準(zhǔn)包裝: | 7 |

| 系列: | Stratix® |

| LAB/CLB數(shù): | 7904 |

| 邏輯元件/單元數(shù): | 79040 |

| RAM 位總計(jì): | 7427520 |

| 輸入/輸出數(shù): | 1203 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 1508-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1508-FBGA(30x30) |

6–8

Altera Corporation

Stratix Device Handbook, Volume 2

July 2005

Architecture

Multiplier Stage

The multiplier stage supports 9

× 9, 18 × 18, or 36 × 36 multiplication.

(The multiplier stage also support smaller multipliers. See “Operational

Modes” on page 6–18 for details.) Based on the data width, a single DSP

block can perform many multiplications in parallel.

The multiplier operands can be signed or unsigned numbers. Two

signals, signa and signb, indicate the representation of the two

operands. For example, a logic 1 on the signa signal indicates that data

A is a signed number; a logic 0 indicates an unsigned number. The result

of the multiplication is signed if any one of the operands is a signed

number, as shown in Table 6–3.

The signa and signb signals affect the entire DSP block. Therefore, all

of the data A inputs feeding the same DSP block must have the same sign

representation. Similarly, all of the data B inputs feeding the same DSP

block must have the same sign representation. The multiplier offers full

precision regardless of the sign representation.

1

By default, the Altera Quartus II software sets the multiplier to

perform unsigned multiplication when the signa and signb

signals are not used.

Pipeline Registers

The output from the multiplier can feed a pipeline register or be

bypassed. You can use pipeline registers for any multiplier size;

pipelining is useful for increasing the DSP block performance,

particularly when using subsequent adder stages.

1

In the DSP block, pipelining improves the performance of

36

× 36 multipliers. For 18 × 18 multipliers and smaller,

pipelining adds latency but does not improve performance.

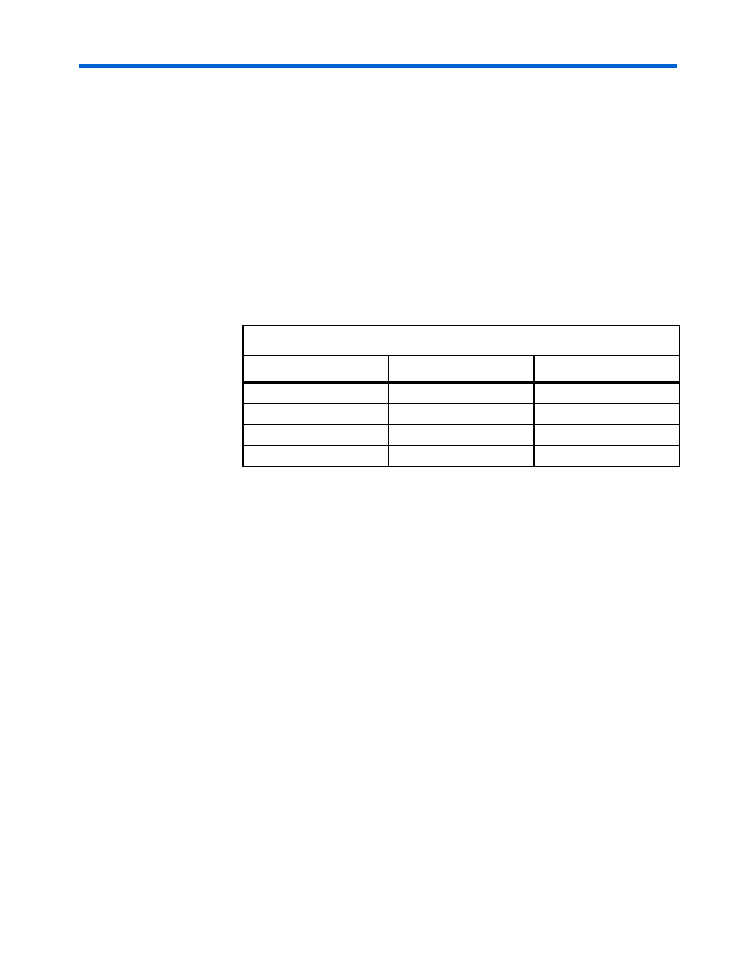

Table 6–3. Multiplier Signed Representation

Data A

Data B

Result

Unsigned

Signed

Unsigned

Signed

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24LC01BT-E/MNY | IC EEPROM 1KBIT 400KHZ 8TDFN |

| A54SX72A-CQ256B | IC FPGA SX-A 108K 256-CQFP |

| EP4SE530H35C4 | IC STRATIX IV FPGA 530K 1152HBGA |

| 24C01CT-E/OT | IC EEPROM 1KBIT 400KHZ SOT23-6 |

| EP4SGX290NF45C4N | IC STRATIX IV FPGA 290K 1932FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP1S80F1508C7 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix I 7904 LABs 1203 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1S80F1508C7ES | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Stratix Device Family Data Sheet |

| EP1S80F1508C7N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Stratix I 7904 LABs 1203 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1S80F1508I5ES | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Stratix Device Family Data Sheet |

| EP1S80F1508I6ES | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Stratix Device Family Data Sheet |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。