- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384280 > EDE5108ABSE (Elpida Memory, Inc.) 512M bits DDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | EDE5108ABSE |

| 廠商: | Elpida Memory, Inc. |

| 英文描述: | 512M bits DDR2 SDRAM |

| 中文描述: | 512M比特DDR2 SDRAM內(nèi)存 |

| 文件頁(yè)數(shù): | 44/66頁(yè) |

| 文件大?。?/td> | 697K |

| 代理商: | EDE5108ABSE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)當(dāng)前第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)

EDE5104ABSE, EDE5108ABSE, EDE5116ABSE

Data Sheet E0323E90 (Ver. 9.0)

44

Posted

WRIT

NOP

CK

/CK

T0

T1

T2

T3

T4

T5

T6

T7

T9

Command

DQS, /DQS

DQ

WL = RL

1 = 4

>

tWR

=

in0

in1

in2

in3

PRE

=

<

tDQSS

Completion of

the Burst Write

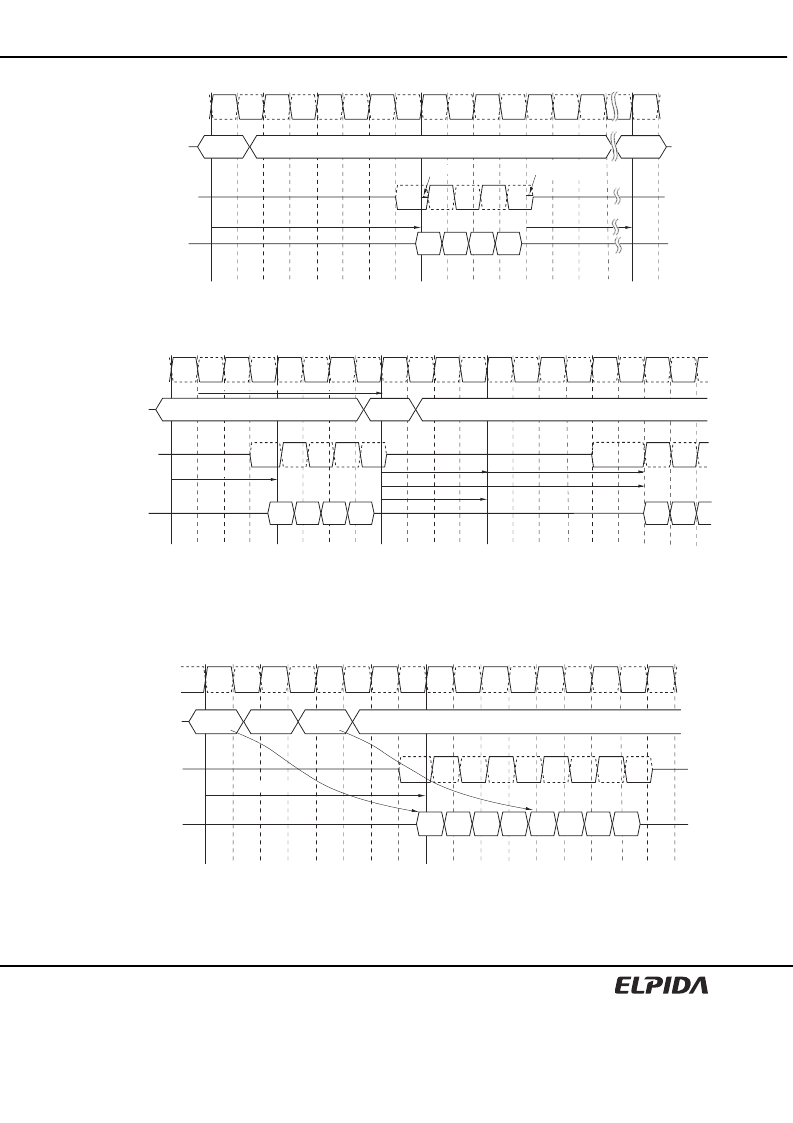

Burst Write Operation (RL = 5, WL = 4, BL = 4 tWR = 3 (AL=2, CL=3))

NOP

CK

/CK

T0

T1

T2

T3

T4

T5

T6

T7

T8

T9

T10

Command

DQS, /DQS

DQ

CL = 3

RL = 5

AL = 2

>

tWTR

=

in0

in2

NOP

in1

in3

Posted

READ

WL = RL –1 = 4

Write to Read = CL - 1 + BL/2 + tWTR (2) = 6

out0

out1

Burst Write Followed by Burst Read (RL = 5, BL = 4, WL = 4, tWTR = 2 (AL=2, CL=3))

The minimum number of clock from the burst write command to the burst read command is CL - 1 + BL/2 + a write

to-read-turn-around-time (tWTR). This tWTR is not a write recovery time (tWR) but the time required to transfer the

4bit write data from the input buffer into sense amplifiers in the array.

NOP

/CK

CK

T0

T1

T2

T3

T4

T5

T6

T7

T8

Command

DQS, /DQS

DQ

in

A0

in

A2

NOP

in

A1

in

A3

in

B0

in

B2

in

B1

in

B3

Posted

WRIT

Posted

WRIT

WL = RL

1 = 4

A

B

Seamless Burst Write Operation (RL = 5, WL = 4, BL = 4)

Enabling a write command every other clock supports the seamless burst write operation. This operation is allowed

regardless of same or different banks as long as the banks are activated.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EDE5108AESK | 512M bits DDR2 SDRAM |

| EDE5108GBSA | 512M bits DDR-II SDRAM |

| EDE5104AESK | 512M bits DDR2 SDRAM |

| EDE5104AESK-4A-E | 512M bits DDR2 SDRAM |

| EDE5104AESK-5C-E | 512M bits DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EDE5108ABSE-4A-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM |

| EDE5108ABSE-5C-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM |

| EDE5108ABSE-AE | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM for HYPER DIMM |

| EDE5108ABSE-AE-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM for HYPER DIMM |

| EDE5108ABSE-BE | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR2 SDRAM for HYPER DIMM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。