- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374140 > CAT35C804A 4K-Bit Secure Access Serial E2PROM PDF資料下載

參數(shù)資料

| 型號: | CAT35C804A |

| 英文描述: | 4K-Bit Secure Access Serial E2PROM |

| 中文描述: | 4K的位安全接入串行E2PROM |

| 文件頁數(shù): | 11/14頁 |

| 文件大?。?/td> | 88K |

| 代理商: | CAT35C804A |

Preliminary

CAT35C804A

11

Doc. No. 25043-00 2/98

then the WRAL instruction. The CAT35C804A will ac-

cept the following commands:

ERAL

ERAL

ERAL

WRAL

An ERAL will be executed

A WRAL will be executed

Both the ERAL and WRAL commands will program/

erase the entire array and will not be blocked by the

memory pointer.

THE PARITY BIT

The UART compatible protocol supports an even parity

bit if the PE pin of the device is set HIGH, otherwise,

there is no parity. If PE is set LOW and the incoming

instruction contains a parity bit, it may be interpreted as

the stop bit. When PE is HIGH, the CAT35C804A

expects a parity bit at the end of every byte. For example,

the RSEQ instruction will look like this:

0 1100 1011 11

0 A15…A8 P1

0 A7…A0 P1

The device then outputs data continuously until it reaches

the end of the memory. Each byte of data contains 9 bits

with the ninth bit being the parity bit. The RSEQ instruc-

tion may be terminated at any time by bringing CS low;

the output will then go to high impedance.

SYSTEM ERRORS

Whenever an error occurs, be it an instruction error

(unknown instruction), or parity error (perhaps caused

by transmission error), the device will stop its operation.

To return to normal operation, the device must be reset

by pulsing CS LOW and then set back to HIGH. Reset-

ting the device will not affect the ENAC, EWEN and

ENBSY status. The error may be determined by entering

the READ STATUS REGISTER (RSR) instruction

immediatly following the reset. The status output is an

8-bit word with the first three bits being 101. This three

bit pattern indicates that the device is functioning nor-

mally. The fourth bit is “1” if a parity error occurred. The

fifth bit is a “1” if an instruction error occurred. The sixth

bit is a “1” if the device is in a program/erase cycle. The

last two bits are reserved for future use.

The reason for the “101” pattern is to distinguish be-

tween an error conditon (DO tri-stated) and a device

busy status. If an error condition exists, it will not respond

to any input instruction from DI. However, if the device is

in a program/erase cycle, it responds to the RSR instruc-

tion by outputting “101 00100”. If RSR is executed at the

end of a program/erase cycle, the output will be “101000

00”.

5074 FHD F09

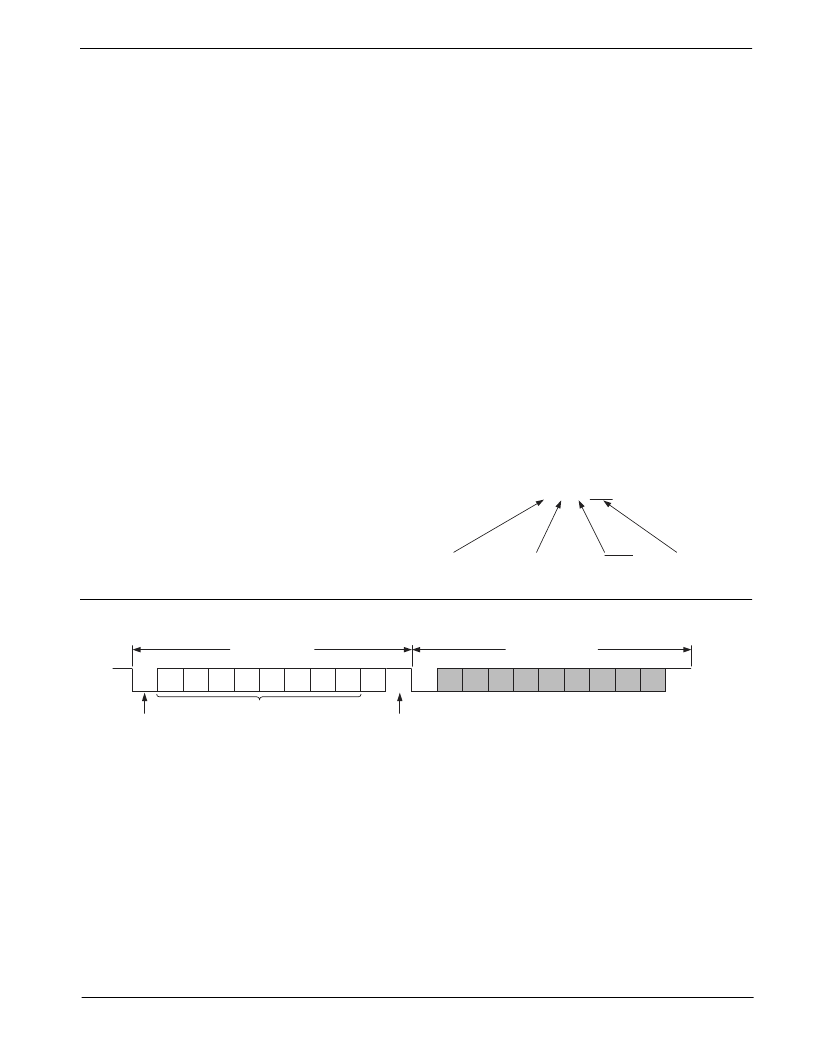

Figure 13. Asynchronous Communication Protocol

PARITY

ERROR

INSTRUCTION

ERROR

RDY/BUSY

STATUS

FUTURE USE

1 0 1 X X X X X

START

BIT

(1)

STOP

BIT

CHARACTER n

CHARACTER n+1

BITS 0–7

35C804 F14

Note:

(1) Parity bit if enabled; skipped if parity disabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT37 | CMOS White LED Driver Boost Converter |

| CAT37EKK-TE7 | CMOS White LED Driver Boost Converter |

| CAT37RD4-TE13 | CMOS White LED Driver Boost Converter |

| CAT37TDI | CMOS White LED Driver Boost Converter |

| CAT4137 | CMOS Boost Converter- White LED Driver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT35C804ACI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial EEPROM |

| CAT35C804ADI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial EEPROM |

| CAT35C804AJATE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:4K-Bit Secure Access Serial E2PROM |

| CAT35C804AJITE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:4K-Bit Secure Access Serial E2PROM |

| CAT35C804AJI-TE13 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。