- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374140 > CAT33C804APA-TE13 4K-Bit Secure Access Serial E2PROM PDF資料下載

參數(shù)資料

| 型號(hào): | CAT33C804APA-TE13 |

| 英文描述: | 4K-Bit Secure Access Serial E2PROM |

| 中文描述: | 4K的位安全接入串行E2PROM |

| 文件頁數(shù): | 13/14頁 |

| 文件大小: | 89K |

| 代理商: | CAT33C804APA-TE13 |

Preliminary

CAT33C804A

13

Doc. No. 25044-00 2/98

1000 0011

Override the memory protection for the next instruction.

READ

Read Memory

1100

[A7–A0]

(x16 organization)

1100 1001

1001

[A15–A8] [A7–A0]

(x8 organization)

Output the contents of the addressed memory location

to the serial port.

WRITE

Write Memory

1100

[A7–A0] [D15–D8] [D7–D0]

(x16 organization)

1100 0001

0001

[A15–A8] [A7–A0] [D7–D0]

(x8 organization)

Write the 8-bit or 16-bit data to the addressed memory

location. After the instruction, address, and data have

been entered, the self-timed program/erase cycle will

start. The addressed memory location will be erased

before data is written. The DO pin may be used to output

the RDY/

BUSY

status by having previously entered the

ENBSY instruction. During the program/erase cycle, DO

will output a LOW for BUSY during this cycle and a HIGH

for READY after the cycle has been completed.

ERASE

Clear Memory

1100

[A7–A0]

(x16 organization)

1100 0000

0000

[A15–A8] [A7–A0]

(x8 organization)

Erase data in the specified memory location (set memory

to “1”). After the instruction and the address have been

entered, the self-timed clear cycle will start. The DO pin

may be used to output the RDY/

BUSY

status by having

previously entered the ENSBY instruction. During the

clear cycle, DO will output a LOW for BUSY during this

cycle and a HIGH for ready after the cycle has been

completed.

ERAL

Clear All

1000

1000 1001

1001

Erase the data of all memory locations (all cells set to

“1”). For protection against inadvertent chip clear, the

ERAL instruction is required to be entered twice.

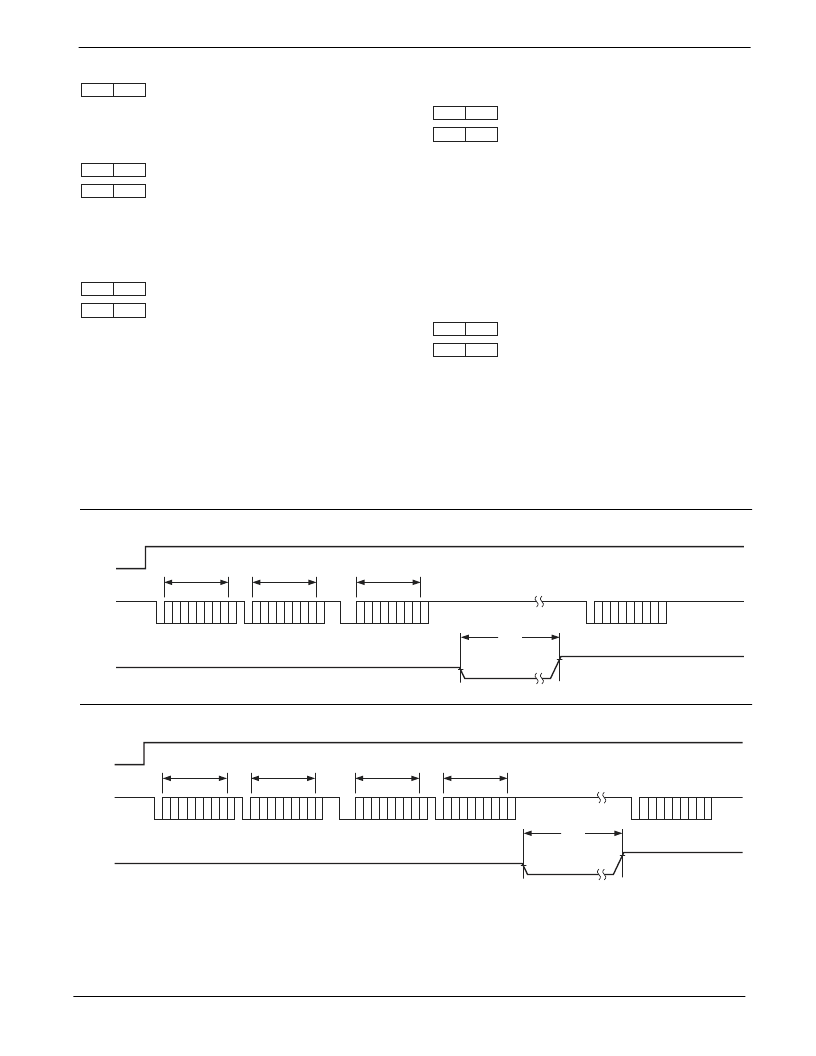

Figure 16. WRAL Timing (x8 Format)

33C804 F17

33C804 F18

Note:

(1)

DO becomes low to indicate busy status if ENBSY was previously executed. If ENBSY was not previously executed, DO will be in the

High-Z condition.

CS

DI

HIGH-Z

DO

OP0–OP7

tEW

BUSY(1)

OP CODE

OP0–OP7

OP CODE

NEXT INSTRUCTION

D0–D7

DATA

Figure 17. WRAL Timing (x16 Format)

CS

DI

HIGH-Z

DO

OP0–OP7

tEW

BUSY(1)

OP CODE

OP0–OP7

OP CODE

NEXT INSTRUCTION

D8–D15

DATA

D0–D7

DATA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT33C804API-TE13 | 4K-Bit Secure Access Serial E2PROM |

| CAT35C104I | 4K-Bit SERIAL E2PROM |

| CAT35C804A | 4K-Bit Secure Access Serial E2PROM |

| CAT37 | CMOS White LED Driver Boost Converter |

| CAT37EKK-TE7 | CMOS White LED Driver Boost Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT33C804APITE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:4K-Bit Secure Access Serial E2PROM |

| CAT33C804API-TE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:4K-Bit Secure Access Serial E2PROM |

| CAT33C804APTE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:4K-Bit Secure Access Serial E2PROM |

| CAT33C804AP-TE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:4K-Bit Secure Access Serial E2PROM |

| CAT33C804BCI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。