- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375310 > AM70PDL129CDH66IS (SPANSION LLC) Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) PDF資料下載

參數(shù)資料

| 型號(hào): | AM70PDL129CDH66IS |

| 廠商: | SPANSION LLC |

| 元件分類: | 存儲(chǔ)器 |

| 英文描述: | Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| 中文描述: | SPECIALTY MEMORY CIRCUIT, PBGA93 |

| 封裝: | 13 X 9 MM, FBGA-93 |

| 文件頁(yè)數(shù): | 17/127頁(yè) |

| 文件大小: | 846K |

| 代理商: | AM70PDL129CDH66IS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)

November 24, 2003

Am70PDL127CDH/Am70PDL129CDH

15

A D V A N C E I N F O R M A T I O N

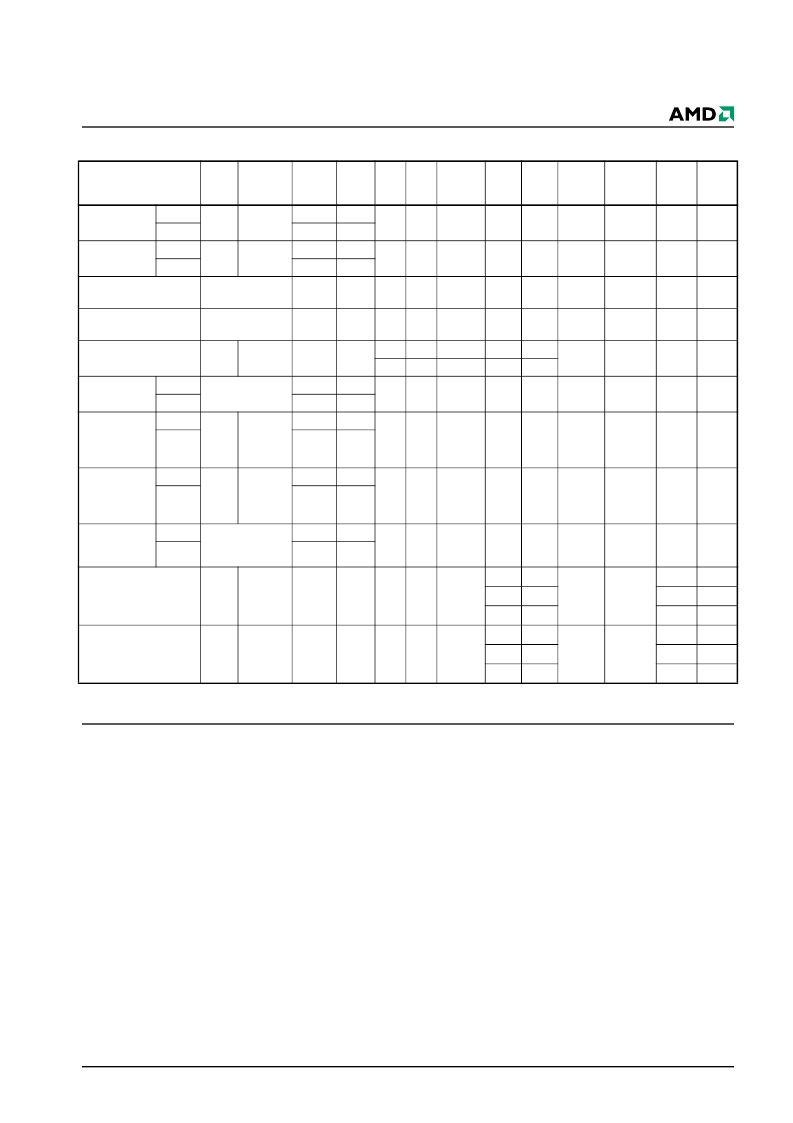

Table 1.

Device Bus Operations

Legend:

L = Logic Low = V

IL

, H = Logic High = V

IH

, V

ID

= 11.5–12.5

V V

HH

= 9.0 ± 0.5 V, X = Don’t Care, SADD = Flash Sector Address, A

IN

=

Address In, D

IN

= Data In, D

OUT

= Data Out

Notes:

1.

Other operations except for those indicated in this column are

inhibited.

Do not apply CE#f1 or 2 = V

IL

, CE#1ps = V

IL

and CE2ps = V

IH

at

the same time.

Don’t care or open LB#s or UB#s.

If WP#/ACC = V

, the boot sectors will be protected. If WP#/ACC

= V

the boot sectors protection will be removed.

If WP#/ACC = V

ACC

(9V), the program time will be reduced by

40%.

The sector protect and sector unprotect functions may also be

implemented via programming equipment. See the “Sector/Sector

Block Protection and Unprotection” section.

2.

3.

4.

5.

6.

If WP#/ACC = V

, the two outermost boot sectors remain

protected. If WP#/ACC = V

, the two outermost boot sector

protection depends on whether they were last protected or

unprotected using the method described in “Sector/Sector Block

Protection and Unprotection”. If WP#/ACC = V

HH,

all sectors will

be unprotected.

Data will be retained in pSRAM.

Data will be lost in pSRAM.

7.

8.

9.

Both CE#f1 inputs may be held low for this operation.

Operation

(Notes 1, 2)

CE#f1

Active

CE#f2

(PDL129

only)

CE#1ps CE2ps OE#

WE#

Addr.

LB#s

(Note

3)

UB#s

(Note

3)

RESET#

WP#/

ACC

(Note 4)

DQ7–

DQ0

DQ15–

DQ8

Read from

Active Flash

(Note 7)

L (H)

H (L)

H

H

L

H

A

IN

X

X

H

L/H

D

OUT

D

OUT

(Note 8)

H

L

Write to Active

Flash

(Note 7)

L (H)

H (L)

H

H

H

L

A

IN

X

X

H

(Note 4)

D

IN

D

IN

(Note 8)

H

L

Standby

V

CC

±

0.3 V

H

H

X

X

X

X

X

V

CC

±

0.3 V

H

High-Z

High-Z

Deep Power-down

Standby

V

CC

±

0.3 V

H

L

X

X

X

X

X

V

CC

±

0.3 V

H

High-Z

High-Z

Output Disable (Note 9)

L (H)

H (L)

L

H

H

H

X

X

X

H

L/H

High-Z

High-Z

H

H

X

X

X

Flash Hardware

Reset

(Note 7)

X

H

H

X

X

X

X

X

L

L/H

High-Z

High-Z

(Note 8)

H

L

Sector Protect

(Notes 6, 10)

(Note 7)

L (H)

H (L)

H

H

H

L

SADD,

A6 = L,

A1 = H,

A0 = L

X

X

V

ID

L/H

D

IN

X

(Note 9)

H

L

Sector

Unprotect

(Notes 5, 9)

(Note 7)

L (H)

H (L)

H

H

H

L

SADD,

A6 = H,

A1 = H,

A0 = L

X

X

V

ID

(Note 6)

D

IN

X

(Note 8)

H

L

Temporary

Sector

Unprotect

(Note 7)

X

H

H

X

X

X

X

X

V

ID

(Note 6)

D

IN

High-Z

(Note 8)

H

L

Read from pSRAM

H

H

L

H

L

H

A

IN

L

L

H

X

D

OUT

D

OUT

H

L

High-Z

D

OUT

L

H

D

OUT

High-Z

Write to pSRAM

H

H

L

H

X

L

A

IN

L

L

H

X

D

IN

D

IN

H

L

High-Z

D

IN

L

H

D

IN

High-Z

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM70PDL129CDH66IT | Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| AM70PDL129CDH85I | Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| AM70PDL129CDH85IS | Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| AM70PDL129CDH85IT | Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| AM75DL9608HG | 64 Megabit (4 M x 16-Bit) and 32 Megabit (2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memories, and |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM70PDL129CDH66IT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| AM70PDL129CDH85I | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| AM70PDL129CDH85IS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| AM70PDL129CDH85IT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

| AM70PDL7BDH66IS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP/XIP) Flash Memory, Data storage MirrorBit Flash, and pSRAM (XIP) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。