- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374039 > ADUC841 (Analog Devices, Inc.) MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU PDF資料下載

參數(shù)資料

| 型號: | ADUC841 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| 中文描述: | MicroConverter的12位ADC和嵌入式高速DAC的62 - kB的閃存微控制器 |

| 文件頁數(shù): | 50/88頁 |

| 文件大小: | 903K |

| 代理商: | ADUC841 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

ADuC841/ADuC842/ADuC843

Rev. 0 | Page 50 of 88

An I

2

C slave can respond to repeated start conditions

without a stop bit in between. This allows a master to

change direction of transfer without giving up the bus.

Note that the repeated start is detected only when a slave

has previously been configured as a receiver.

On-chip filtering rejects <50 ns spikes on the SDATA and

the SCLOCK lines to preserve data integrity.

DV

DD

I

2

C

MASTER

I

2

C

SLAVE 1

I

2

C

SLAVE 2

0

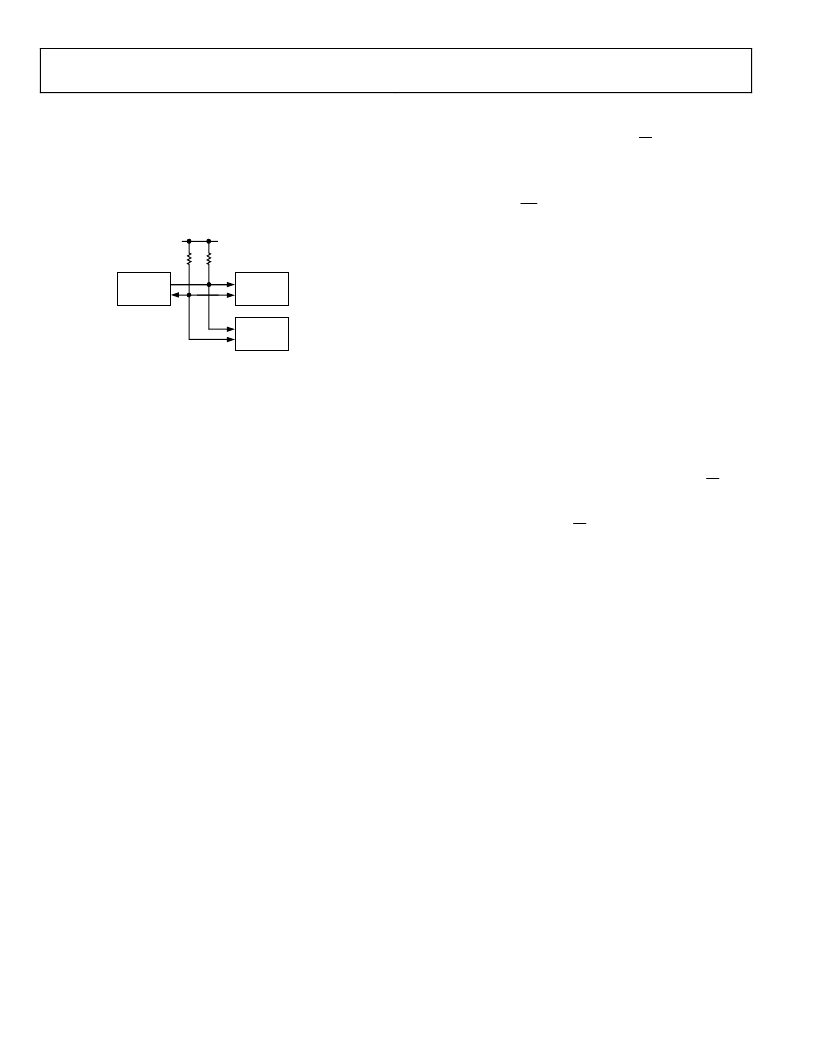

Figure 55. Typical I

2

C System

Software Master Mode

The ADuC841/ADuC842/ADuC843 can be used as I

2

C master

devices by configuring the I

2

C peripheral in master mode and

writing software to output the data bit by bit. This is referred to

as a software master. Master mode is enabled by setting the I2CM

bit in the I2CCON register.

To transmit data on the SDATA line, MDE must be set to enable

the output driver on the SDATA pin. If MDE is set, the SDATA

pin is pulled high or low depending on whether the MDO bit is

set or cleared. MCO controls the SCLOCK pin and is always

configured as an output in master mode. In master mode, the

SCLOCK pin is pulled high or low depending on the whether

MCO is set or cleared.

To receive data, MDE must be cleared to disable the output

driver on SDATA. Software must provide the clocks by toggling

the MCO bit and reading the SDATA pin via the MDI bit. If

MDE is cleared, MDI can be used to read the SDATA pin. The

value of the SDATA pin is latched into MDI on a rising edge of

SCLOCK. MDI is set if the SDATA pin was high on the last

rising edge of SCLOCK. MDI is clear if the SDATA pin was low

on the last rising edge of SCLOCK.

Software must control MDO, MCO, and MDE appropriately to

generate the start condition, slave address, acknowledge bits,

data bytes, and stop conditions. These functions are described

in Application Note uC001.

Hardware Slave Mode

After reset, the ADuC841/ADuC842/ADuC843 default to

hardware slave mode. The I

2

C interface is enabled by clearing

the SPE bit in SPICON (this is not necessary if the MSPI bit is

set). Slave mode is enabled by clearing the I2CM bit in I2CCON.

The parts have a full hardware slave. In slave mode, the I

2

C

address is stored in the I2CADD register. Data received or to be

transmitted is stored in the I2CDAT register.

Once enabled in I

2

C slave mode, the slave controller waits for a

start condition. If the part detects a valid start condition, fol-

lowed by a valid address, followed by the R/W bit, the I2CI

interrupt bit is automatically set by hardware. The I

2

C peripheral

generates a core interrupt only if the user has pre-configured

the I

2

C interrupt enable bit in the IEIP2 SFR as well as the

global interrupt bit, EA, in the IE SFR. i.e.,

;Enabling I2C Interrupts for the ADuC842

MOV IEIP2,#01h

SETB EA

; enable I2C interrupt

An autoclear of the I2CI bit is implemented on the parts so that

this bit is cleared automatically on a read or write access to the

I2CDAT SFR.

MOV I2CDAT, A

MOV A, I2CDAT

If for any reason the user tries to clear the interrupt more than

once, i.e., access the data SFR more than once per interrupt, then

the I

2

C controller will halt. The interface will then have to be

reset using the I2CRS bit.

; I2CI auto-cleared

; I2CI auto-cleared

The user can choose to poll the I2CI bit or to enable the inter-

rupt. In the case of the interrupt, the PC counter vectors to

003BH at the end of each complete byte. For the first byte, when

the user gets to the I2CI ISR, the 7-bit address and the R/W bit

appear in the I2CDAT SFR.

The I2CTX bit contains the R/W bit sent from the master. If

I2CTX is set, the master is ready to receive a byte. Therefore the

slave will transmit data by writing to the I2CDAT register. If

I2CTX is cleared, the master is ready to transmit a byte. There-

fore the slave will receive a serial byte. Software can interrogate

the state of I2CTX to determine whether it should write to or

read from I2CDAT.

Once the part has received a valid address, hardware holds

SCLOCK low until the I2CI bit is cleared by software. This

allows the master to wait for the slave to be ready before

transmitting the clocks for the next byte.

The I2CI interrupt bit is set every time a complete data byte is

received or transmitted, provided it is followed by a valid ACK.

If the byte is followed by a NACK, an interrupt is not generated.

The part continues to issue interrupts for each complete data

byte transferred until a stop condition is received or the inter-

face is reset.

When a stop condition is received, the interface resets to a state

in which it is waiting to be addressed (idle). Similarly, if the

interface receives a NACK at the end of a sequence, it also

returns to the default idle state. The I2CRS bit can be used to

reset the I

2

C interface. This bit can be used to force the interface

back to the default idle state.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADUC841BCP62-3 | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| ADUC841BCP62-5 | Cable Gland (Clamp); Connector Shell Size:10SL, 12S; Thread Size:5/8-24; Approval Categories:MIL-C-5015; Series:97 RoHS Compliant: Yes |

| ADUC841BCP8-3 | 10-823955-004 |

| ADUC841BCP8-5 | Cable Gland (Clamp); Connector Shell Size:14, 14S; Thread Size:3/4-20; Body Material:Zinc Alloy |

| ADUC841BS62-3 | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADUC841BCP32-5 | 制造商:Analog Devices 功能描述:MICROCONVERTER 1-CYCLE VERSION ADUC829 - Trays |

| ADUC841BCP62-3 | 制造商:Analog Devices 功能描述:MCU 8-Bit ADuC8xx 8052 CISC 62KB Flash 3V 56-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:8BIT CISC 62KB FLASH 20MHZ 3.3V 56LFCSP - Bulk |

| ADUC841BCP62-5 | 制造商:Analog Devices 功能描述:MCU 8-Bit ADuC8xx 8052 CISC 62KB Flash 5V 56-Pin LFCSP EP |

| ADUC841BCP8-3 | 制造商:Analog Devices 功能描述:MCU 8-bit ADuC8xx 8052 CISC 62KB Flash 3V 56-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:8BIT CISC 62KB FLASH 20MHZ 3.3V 56LFCSP - Bulk |

| ADUC841BCP8-5 | 制造商:AD 制造商全稱:Analog Devices 功能描述:MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。