- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374032 > ADSP-2100A (Analog Devices, Inc.) ADSP-2100 Family DSP Microcomputers PDF資料下載

參數(shù)資料

| 型號: | ADSP-2100A |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | ADSP-2100 Family DSP Microcomputers |

| 中文描述: | 的ADSP - 2100系列DSP的微機(jī) |

| 文件頁數(shù): | 21/64頁 |

| 文件大?。?/td> | 668K |

| 代理商: | ADSP-2100A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

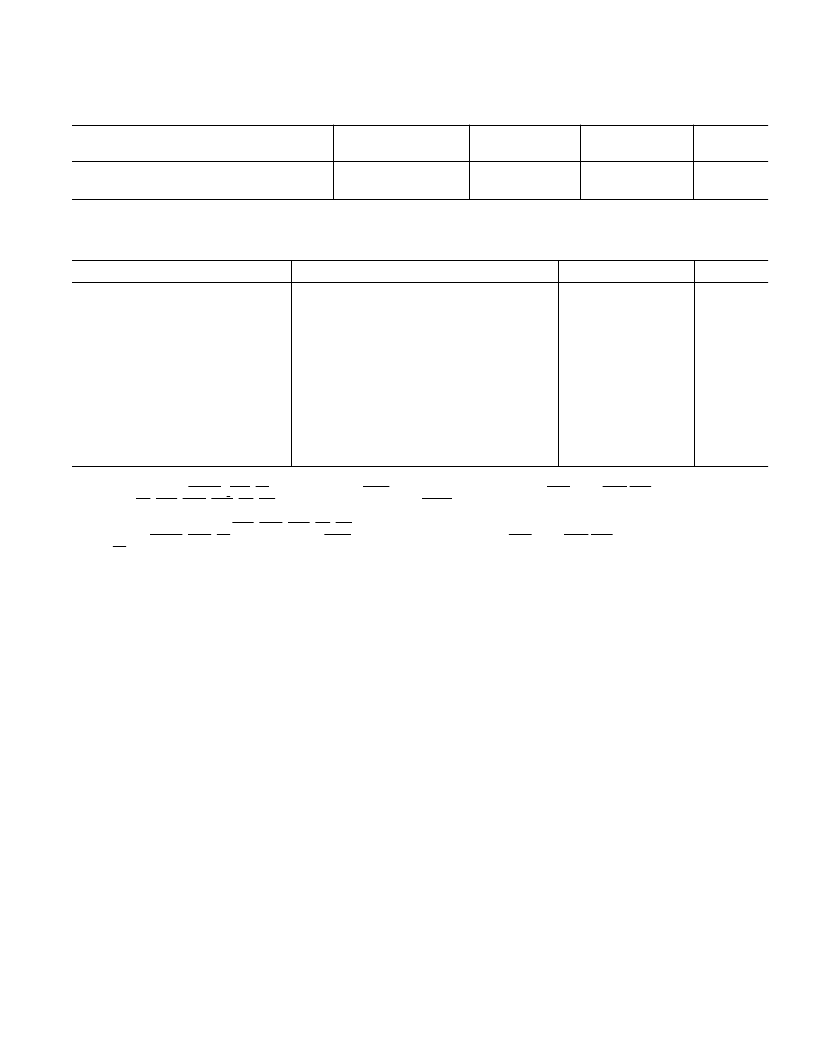

ADSP-2111–SPECIFICATIONS

RECOMMENDEDOPERATINGCONDITIONS

K Grade

Min

B Grade

Min

T Grade

Min

Parameter

Max

Max

Max

Unit

V

DD

T

AMB

Supply Voltage

Ambient Operating T emperature

4.50

0

5.50

+70

4.50

–40

5.50

+85

4.50

–55

5.50

+125

V

°

C

See “Environmental Conditions” for information on thermal specifications.

ELECTRICAL CHARACTERISTICS

Parameter

T est Conditions

Min

Max

Unit

V

IH

V

IH

V

IL

V

OH

Hi-Level Input Voltage

3, 5

Hi-Level CLK IN Voltage

Lo-Level Input Voltage

1, 3

Hi-Level Output Voltage

2, 3, 7

@ V

DD

= max

@ V

DD

= max

@ V

DD

= min

@ V

DD

= min, I

OH

= –0.5 mA

@ V

DD

= min, I

OH

= –100

μ

A

8

@ V

DD

= min, I

OL

= 2 mA

@ V

DD

= max, V

IN

= V

DD

max

@ V

DD

= max, V

IN

= 0V

@ V

DD

= max, V

IN

= V

DD

max

6

@ V

DD

= max, V

IN

= 0V

6

@ V

IN

= 2.5 V, f

IN

= 1.0 MHz, T

AMB

= 25

°

C

@ V

IN

= 2.5 V, f

IN

= 1.0 MHz, T

AMB

= 25

°

C

2.0

2.2

V

V

V

V

V

V

μ

A

μ

A

μ

A

μ

A

pF

pF

0.8

2.4

V

DD

– 0.3

V

OL

I

IH

I

IL

I

OZH

I

OZL

C

I

C

O

Lo-Level Output Voltage

2, 3, 7

Hi-Level Input Current

1

Lo-Level Input Current

1

T ristate Leakage Curren

4

T ristate Leakage Current

4

Input Pin Capacitance

1, 8, 9

Output Pin Capacitance

4, 8, 9, 10

0.4

10

10

10

10

8

8

NOT ES

Input-only pins: CLK IN,

RESET

, I

RQ2

,

BR

, MMAP, DR1, DR0,

HSEL

, HSIZE, BMODE, HMD0, HMD1,

HRD

/HRW,

HWR

/

HDS

, HA2/ALE, HA1-0.

2

Output pins:

BG

,

PMS

,

DMS

,

BMS

,

RD

,

WR

, A0–A13, CLK OUT , DT 1, DT 0,

HACK

, FL2-0.

3

Bidirectional pins: D0–D23, SCLK 1, RFS1, T FS1, SCLK 0, RFS0, T FS0, HD0–HD15/HAD0–HAD15.

4

T ristatable pins: A0–A13, D0–D23,

PMS

,

DMS

,

BMS

,

RD

,

WR

, DT 1, SCLK 1, RSF1, T FS1, DT 0, SCLK 0, RFS0, T FS0, HD0–HD15/HAD0–HAD15.

5

Input-only pins:

RESET

,

IRQ2

,

BR

, MMAP, DR1, DR0,

HSEL

, HSIZE, BMODE, HMD0, HMD1,

HRD

/HRW,

HWR

/

HDS

, HA2/ALE, HA1-0.

6

0 V on

BR

, CLK IN Active (to force tristate condition).

7

Although specified for T T L outputs, all ADSP-2111 outputs are CMOS-compatible and will drive to V

DD

and GND, assuming no dc loads.

8

Guaranteed but not tested.

9

Applies to ADSP-2111 PGA and PQFP packages.

10

Output pin capacitance is the capacitive load for any three-stated output pin.

Specifications subject to change without notice.

ABSOLUT E MAX IMUM RAT INGS*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

Input Voltage . . . . . . . . . . . . . . . . . . . . . –0.3 V to V

DD

+ 0.3 V

Output Voltage Swing . . . . . . . . . . . . . . –0.3 V to V

+ 0.3 V

Operating T emperature Range (Ambient) . . . –55oC to +125oC

Storage T emperature Range . . . . . . . . . . . . . –65oC to +150oC

Lead T emperature (10 sec) PGA . . . . . . . . . . . . . . . . . +300oC

Lead T emperature (5 sec) PQFP . . . . . . . . . . . . . . . . . +280oC

*Stresses greater than those listed above may cause permanent damage to the

device. T hese are stress ratings only, and functional operation of the device at these

or any other conditions greater than those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect device reliability.

ADSP-21xx

REV. B

–21–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-2101 | 16-Bit Fixed-Point DSP(16位定點(diǎn)型DSP) |

| ADSP-21060KB-160 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21060 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21060L | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21060LAB-160 | ADSP-2106x SHARC DSP Microcomputer Family |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2100AJG | 制造商:AD 制造商全稱:Analog Devices 功能描述:12.5 MIPS DSP Microprocessor |

| ADSP-2100AJP | 制造商:AD 制造商全稱:Analog Devices 功能描述:12.5 MIPS DSP Microprocessor |

| ADSP-2100AKG | 制造商:AD 制造商全稱:Analog Devices 功能描述:12.5 MIPS DSP Microprocessor |

| ADSP-2100AKP | 制造商:AD 制造商全稱:Analog Devices 功能描述:12.5 MIPS DSP Microprocessor |

| ADSP-2100ASG | 制造商:AD 制造商全稱:Analog Devices 功能描述:12.5 MIPS DSP Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。