- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374016 > ADMCF340 (Analog Devices, Inc.) DashDSPTM 64-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End PDF資料下載

參數(shù)資料

| 型號(hào): | ADMCF340 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | DashDSPTM 64-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| 中文描述: | DashDSPTM 64無鉛閃存混合信號(hào)增強(qiáng)的DSP與模擬前端 |

| 文件頁數(shù): | 10/40頁 |

| 文件大小: | 415K |

| 代理商: | ADMCF340 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

REV. 0

ADMCF340

–10–

SPORTs can receive and transmit an entire circular buffer of

data with only one overhead cycle per data-word. An interrupt

is generated after a data buffer transfer.

SPORT0 has one pin, SCLK0, shared with SPORT1. Dur-

ing a boot phase (SPORT1 Boot Mode enabled by a bit in

the MODECTRL Register), the serial clock of SPORT1 is

externally available. The serial clock of SPORT0 is exter-

nally available when the SPORT1 is configured in UART

Mode.

SPORT0 can be configured as SPI port (master mode only).

Refer to Table XI for more information. The clock phase and

polarity are programmable through the MODECTRL Register.

Refer to Table XI for pin configuration.

SPORT0 has a multichannel interface to selectively receive

and transmit a 24-word or 32-word time division multiplexed

serial bitstream.

SPORT1 is the default port for program/data memory boot

loading and for the development tools interface. The DT1/FL1

Pin can be configured as the SROM/E

2

prom

reset signal.

The ADMCF340 is available in a 64-lead LQFP package.

PIN FUNCTION DESCRIPTION

Table I. Pin List

Pin Group

Name

# of

Pins

Input/

Output

Function

PWMPOL

PWMSR

1

1

I

I

PWM Polarity

PWM Switched

Reluctance Mode

Processor Reset Input

Serial Port 1 Pins

(DT1/FL1, DR1)

Serial Port 0 Pins

(DT0, DR0, RFS0,

TFS0, SCLK1/

SCLK0

2

)

Processor Clock

Output

External Clock or

Quart Crystal

Connection Point

Digital I/O Port Pins

Digital I/O Port Pins

Auxiliary PWM

Outputs

PWM Outputs

PWM Trip Signal

I

SENSE

Inputs

Analog Inputs

Auxiliary Analog Inputs

ADC Constant

Current Source

Power Supply

Ground

RESET

SPORT1

1

1

2

I

I/O

SPORT0

1

5

I/O

CLKOUT

1

1

1

I/O

CLKIN, XTAL

2

I/O

PORTA0–PORTA8

1

9

PORTB0–PORTB15 16

AUX0–AUX1

1

I/O

I/O

O

2

AH-CL

PWMTRIP

V1 to V3

I

SENSE1

to

I

SENSE3

VAUX0-VAUX7

ICONST

6

1

3

3

7

1

O

I

I

I

I

O

V

DD

GND

3

3

I

I

NOTES

1

Multiplexed pins, individually selectable through PORTA_SELECT and

PORTA_DATA Registers.

2

SCLK1/SCLK0 multiplexed signals. Selectable through MODECTRL

Register Bit 4.

INTERRUPT OVERVIEW

The ADMCF340 can respond to 34 different interrupt sources

with minimal overhead, seven of which are internal DSP core

interrupts and 27 are from the motor control peripherals. The seven

DSP core interrupts are SPORT1 receive (or

IRQ0

) and transmit

(or

IRQ1

), SPORT0 receive and transmit, the internal timer,

and two software interrupts. The motor control peripheral

interrupts are the 25 programmable I/Os and two from the PWM

(PWMSYNC pulse and

PWMTRIP

). All motor control interrupts

are multiplexed into the DSP core through the peripheral

IRQ2

interrupt. The interrupts are internally prioritized and individually

maskable. A detailed description of the entire interrupt system of

the ADMCF340 is presented later, following a more detailed

description of each peripheral block.

MEMORY MAP

The ADMCF340 has two distinct memory types: program

and data. In general, program memory contains user code and

coefficients, while the data memory is used to store variables and

data during program execution. Three kinds of program memory are

provided on the ADMCF340: RAM, ROM, and FLASH. The

motor control peripherals are memory mapped into a region of the

data memory space starting at 0x2000. The complete program and

data memory maps are given in Tables II and III, respectively.

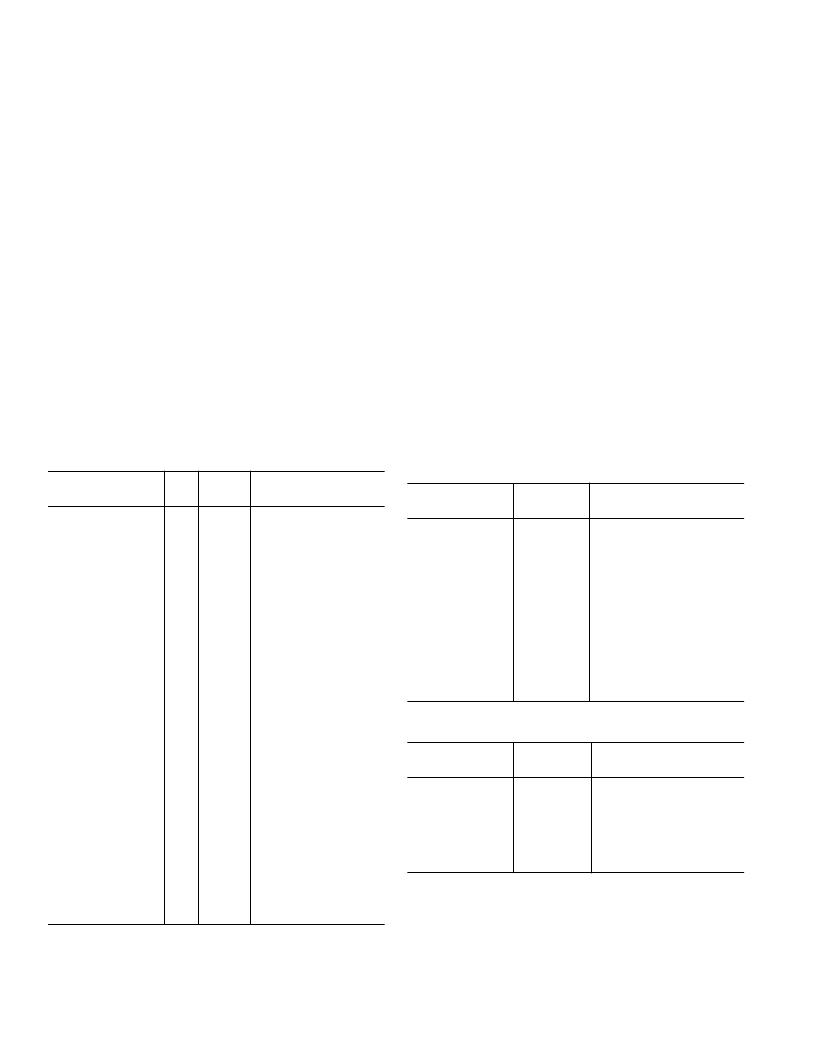

Table II. Program Memory Map

Memory

Type

Address Range

Function

0x0000–0x002F

0x0030–0x01FF

0x0200–0x07FF

0x0800–0x17FF

0x1800–0x1FFF

0x2000–0x20FF

RAM

RAM

Internal Vector Table

User Program Memory

Reserved

Reserved Program Memory

Reserved

User Program Memory

Sector 0

User Program Memory

Sector 1

User Program Memory

Sector 2

Reserved

ROM

FLASH

0x2100–0x21FF

FLASH

0x2200–0x2FFF

FLASH

0x3000–0x3FFF

Table III. Data Memory Map

Memory

Type

Address Range

Function

0x0000–0x1FFF

0x2000–0x20FF

0x2100–0x37FF

0x3800–0x39FF

0x3A00–0x3BFF

0x3C00–0x3FFF

Reserved

Memory Mapped Registers

Reserved

User Data Memory

Reserved

Memory Mapped Registers

RAM

RAM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADMCF340BST | DashDSPTM 64-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF340-EVALKIT | Circular Connector; No. of Contacts:7; Series:MS27497; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:10; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:10-99 RoHS Compliant: No |

| ADMCF341 | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF341BR | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF341-EVALKIT | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADMCF340BST | 制造商:AD 制造商全稱:Analog Devices 功能描述:DashDSPTM 64-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF340-EVALKIT | 制造商:AD 制造商全稱:Analog Devices 功能描述:DashDSPTM 64-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF340XSTB | 制造商:Analog Devices 功能描述: |

| ADMCF341 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF341BR | 制造商:Analog Devices 功能描述:DSP Fixed-Point/Floating-Point 16-Bit 20MHz 20MIPS 28-Pin SOIC W T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。