- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373994 > ADL5390ACPZ-WP1 (Analog Devices, Inc.) RF/IF Vector Multiplier PDF資料下載

參數(shù)資料

| 型號(hào): | ADL5390ACPZ-WP1 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | RF/IF Vector Multiplier |

| 中文描述: | 射頻中頻向量乘法器/ |

| 文件頁(yè)數(shù): | 20/24頁(yè) |

| 文件大?。?/td> | 716K |

| 代理商: | ADL5390ACPZ-WP1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

ADL5390

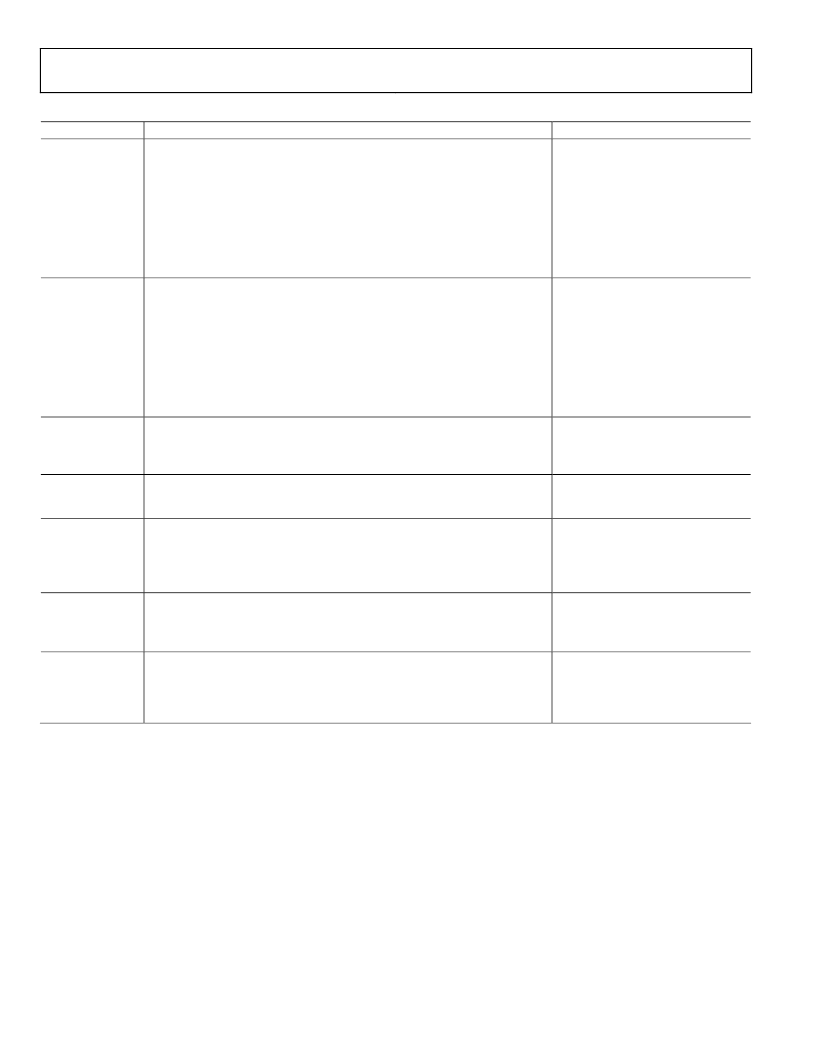

Table 4. Evaluation Board Configuration Options

Component

Function

R7, R9, R11, R14,

R15, R19, R20,

R21, C15, C19,

W3, W4

baseband drive, the Potentiometer R11 can be used to provide a bias level to

the unused input (install either W3 or W4).

Rev. 0 | Page 20 of 24

Default Conditions

R7, R9 = not installed

R11 = potentiometer, 2 k, 10 turn

(Bourns)

R14 = 4 k (size 0603)

R15 = 44 k (size 0603)

R19, R20, R21 = 0 (size 0603)

C15, C19 = 0.1 μF

(Size 0603)

W3 = jumper (installed)

W4 = jumper (open)

R1, R3 = not installed

R10 = potentiometer, 2 k, 10 turn

(Bourns)

R12 = 4 k (size 0603)

R13 = 44 k (size 0603)

R16, R17, R18 = 0

(size 0603)

C16, C20 = 0.1 μF (size 0603)

W1 = jumper (installed)

W2 = jumper (open)

C11, C12 = not installed

I Channel Baseband Interface. Resistors R7 and R9 may be installed to

accommodate a baseband source that requires a specific terminating

impedance. Capacitors C15 and C19 are bypass capacitors. For single-ended

R1, R3, R10, R12,

R13, R16, R17,

R18, C16, C20,

W1, W2

Q Channel Baseband Interface. See the I Channel Baseband Interface section.

C11, C12

Baseband Low-Pass Filtering. By adding capacitor C11 between QFLP and

QFLM, and capacitor C12 between IFLP and IFLM, the 3 dB low-pass corner

frequency of the baseband interface can be reduced from 230 MHz (nominal)

as given by the equation in the Evaluation Board section.

Output Interface. The 1:1 balun transformer, T1, converts the 50 differential

output to 50 single-ended. C17 and C18 are dc blocks. L3 and L4 provide dc

bias for the output.

I and Q Channel RF Input Interface. The single-ended impedance to the

ADL5390 RF inputs is 200 . Shunt terminations R2 and R22 of 66.5 bring the

impedances to 50 . C2 and C5 are dc blocks. C1 and C6 are used to ac-couple

the unused side of the differential inputs to common.

T1, C17, C18, L3,

L4

C17, C18 = 10 nF (size 0603)

T1 = ETC1-1-13 (M/A-COM)

L3, L4 = 120 nH (size 0603)

C2 = C1 = 10 nF (size 0603)

R2 = 66.5

10 (size 0603)

C5 = C6 = 10 nF (size 0603)

R22 = 66.5

10 (size 0603)

R4, R6, R5 = 0

(size 0603)

C4, C7 C9 = 0.1uF (size 0603)

C3, C8, C10 = 100 pF (size 0603)

R8 = 10 k (size 0603)

SW1 = SPDT (Position A, output

enabled)

C2, C1, R2

C5, C6, R22

R4, R6, R5, C4, C7

C9, C3, C8, C10

Power Supply Decoupling.

R8, SW1

Output Disable Interface. The output stage of the ADL5390 is disabled by

applying a high voltage to the DSOP pin by moving SW1 to Position B. The

output stage is enabled moving SW1 to Position A. The output disable

function can also be exercised by applying an external high or low voltage to

the DSOP SMA connector with SW1 in Position A.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADL5390 | RF/IF Vector Multiplier |

| ADL5391 | DC to 2.0 GHz Multiplier |

| ADL5391ACPZ-R2 | DC to 2.0 GHz Multiplier |

| ADL5391ACPZ-R7 | DC to 2.0 GHz Multiplier |

| ADL5391ACPZ-WP | DC to 2.0 GHz Multiplier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADL5390-EVAL | 制造商:Analog Devices 功能描述:EVALUATION BOARD FOR RF/IF VECTOR MULTIPLIER 制造商:Analog Devices 功能描述:EVALUATION BOARD FOR ADL5390 - Bulk |

| ADL5390-EVALZ | 制造商:Analog Devices 功能描述:Evaluation Board For ADL5390 制造商:Analog Devices 功能描述:EVALUATION BOARDS - Bulk |

| ADL5391 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DC to 2.0 GHz Multiplier |

| ADL5391ACPZ | 制造商:Analog Devices 功能描述:IC, MULTIPLIER, 2.0GHZ, 16LFCSP 制造商:Analog Devices 功能描述:IC, MULTIPLIER, 2.0GHZ, 16LFCSP; IC Function:Analogue Multiplier; Brief Features:3 dB bandwidth of 2 GHz; Supply Voltage Min:4.5V; Supply Voltage Max:5.5V; Operating Temperature Min:-40C; Operating Temperature Max:85C; Digital IC ;RoHS Compliant: Yes |

| ADL5391ACPZ-R2 | 制造商:Analog Devices 功能描述:DC TO 2.0 GHZ MULTIPLIER - Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。