- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373972 > AD9984AKSTZ-170 (ANALOG DEVICES INC) High Performance 10-Bit Display Interface PDF資料下載

參數(shù)資料

| 型號(hào): | AD9984AKSTZ-170 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 其它接口 |

| 英文描述: | High Performance 10-Bit Display Interface |

| 中文描述: | SPECIALTY INTERFACE CIRCUIT, PQFP80 |

| 封裝: | ROHS COMPLIANT, MS-026BEC, LQFP-80 |

| 文件頁(yè)數(shù): | 32/44頁(yè) |

| 文件大小: | 490K |

| 代理商: | AD9984AKSTZ-170 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

AD9984A

0x12—Bit[5] Hsync Input Polarity Override

This bit determines whether the chip selects the Hsync input

polarity or if it is specified. Setting this bit to 0 allows the chip

to automatically select the polarity of the input Hsync. Setting it

to 1 indicates that Bit 4 of Register 0x12 specifies the polarity.

Power-up default is 0.

Rev. 0 | Page 32 of 44

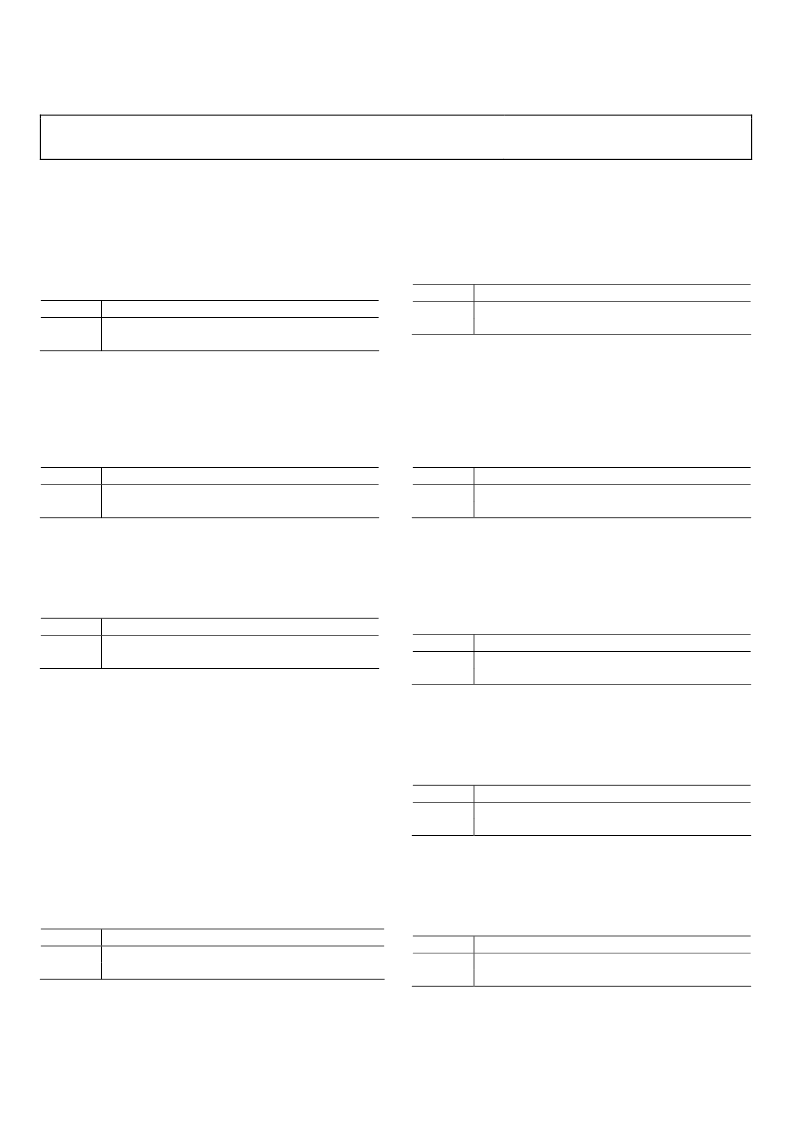

Table 20. Hsync Input Polarity Override Bit

Value

Result

0

Hsync polarity determined by chip.

1

Hsync polarity determined by user (Register 0x12, Bit 4).

0x12—Bit[4] Hsync Input Polarity

If Bit 5 of Register 0x12 is 1, the value of this bit specifies the

polarity of the input Hsync. Setting this bit to 0 indicates a

negative Hsync input polarity. Setting this bit to 1 indicates a

positive Hsync input polarity. Power-up default is 1.

Table 21. Hsync Input Polarity Bit

Value

Result

0

Hsync input polarity is negative.

1

Hsync input polarity is positive.

0x12—Bit[3] Hsync Output Polarity

This bit sets the polarity of the Hsync output (HSOUT). Setting

this bit to 0 indicates a negative HSOUT polarity. Setting this bit

to 1 indicates a positive HSOUT polarity.

Table 22. Hsync Output Polarity Bit

Value

Result

0

HSOUT polarity is negative.

1

HSOUT polarity is positive.

0x13—Bits[7:0] Hsync Duration

This 8-bit register sets the duration of the HSOUT pulse. The

leading edge of the Hsync output is triggered by the internally

generated, phase-adjusted, PLL feedback clock. The AD9984A

then counts a number of pixel clocks equal to the value in this

register. This triggers the trailing edge of HSOUT, which is also

phase-adjusted.

VSYNC CONTROL

0x14—Bit[7] Vsync Source Override

This bit is the active Vsync override. Setting this to 0 allows the

chip to determine the active Vsync source, setting it to 1 uses

Bit 6 of Register 0x14 to determine the active Vsync source.

Power-up default value is 0.

Table 23. Vsync Source Override Bit

Value

Result

0

Vsync source determined by chip.

1

Vsync source determined by user (Register 0x14, Bit 6).

0x14—Bit[6] Vsync Source Select

This bit selects the source of the Vsync for sync processing only

if Bit 7 of Register 0x14 is set to 1. Setting Bit 6 to 0 specifies the

Vsync from the input pin. Setting it to 1 selects Vsync from the

sync separator. Power-up default is 0.

Table 24. Vsync Source Select Bit

Value

Result

0

Vsync from VSYNCx input pin.

1

Vsync from sync separator.

0x14—Bit[5] Vsync Input Polarity Override

This bit sets whether the chip selects the Vsync input polarity or

if it is specified. Setting this bit to 0 allows the chip to

automatically select the polarity of the input Vsync. Setting this

bit to 1 indicates that Bit 4 of Register 0x14 specifies the

polarity. Power-up default is 0.

Table 25. Vsync Input Polarity Override Bit

Value

Result

0

Vsync polarity determined by chip.

1

Vsync polarity determined by user (Register 0x14, Bit 4).

0x14—Bit[4] Vsync Input Polarity

If Bit 5 of Register 0x14 is 1, the value of this bit specifies the

polarity of the input Vsync. Setting this bit to 0 indicates a

negative Vsync input polarity. Setting this bit to 1 indicates a

positive Vsync input polarity. Power-up default is 1.

Table 26. Vsync Input Polarity Bit

Value

Result

0

Vsync input polarity is negative.

1

Vsync input polarity is positive.

0x14—Bit[3] Vsync Output Polarity

This bit sets the polarity of the Vsync output (VSOUT). Setting

this bit to 0 indicates a negative VSOUT polarity. Setting this bit

to 1 indicates a positive VSOUT polarity. Power-up default is 1.

Table 27. Vsync Output Polarity Bit

Value

Result

0

VSOUT polarity is negative.

1

VSOUT polarity is positive.

0x14—Bit[2] Vsync Filter Enable

This bit enables the Vsync filter allowing precise placement of

the Vsync with respect to the Hsync and facilitating the correct

operation of the Hsyncs/Vsync count.

Table 28. Vsync Filter Enable Bit

Value

Result

0

Vsync filter disabled.

1

Vsync filter enabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9984APCBZ | High Performance 10-Bit Display Interface |

| AD9985A | 110 MSPS/140 MSPS Analog Interface for Flat Panel Displays |

| AD9985ABSTZ-110 | 110 MSPS/140 MSPS Analog Interface for Flat Panel Displays |

| AD9985AKSTZ-110 | 110 MSPS/140 MSPS Analog Interface for Flat Panel Displays |

| AD9985AKSTZ-140 | 110 MSPS/140 MSPS Analog Interface for Flat Panel Displays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9984APCBZ | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Performance 10-Bit Display Interface |

| AD9984KSTZ-110 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9984KSTZ-140 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9984KSTZ-170 | 制造商:Analog Devices 功能描述: |

| AD9985 | 制造商:AD 制造商全稱:Analog Devices 功能描述:110 MSPS/140 MSPS Analog Interface for Flat Panel Displays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。