- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373944 > AD8332-EVAL (Analog Devices, Inc.) Ultralow Noise VGAs with Preamplifier and Programmable RIN PDF資料下載

參數(shù)資料

| 型號(hào): | AD8332-EVAL |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Ultralow Noise VGAs with Preamplifier and Programmable RIN |

| 中文描述: | 超低噪聲的VGA前置放大器和可編程與房地產(chǎn)經(jīng)紀(jì)人 |

| 文件頁數(shù): | 24/32頁 |

| 文件大?。?/td> | 482K |

| 代理商: | AD8332-EVAL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

AD8331/AD8332

Table 4. Clamp Resistor Values

Clamp Level

(V p-p)

Rev. C | Page 24 of 32

Clamp Resistor Value (k)

HILO = LO

1.21

2.74

4.75

7.5

11

16.9

26.7

49.9

100

HILO = HI

2.21

4.02

6.49

9.53

14.7

23.2

39.2

73.2

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.4

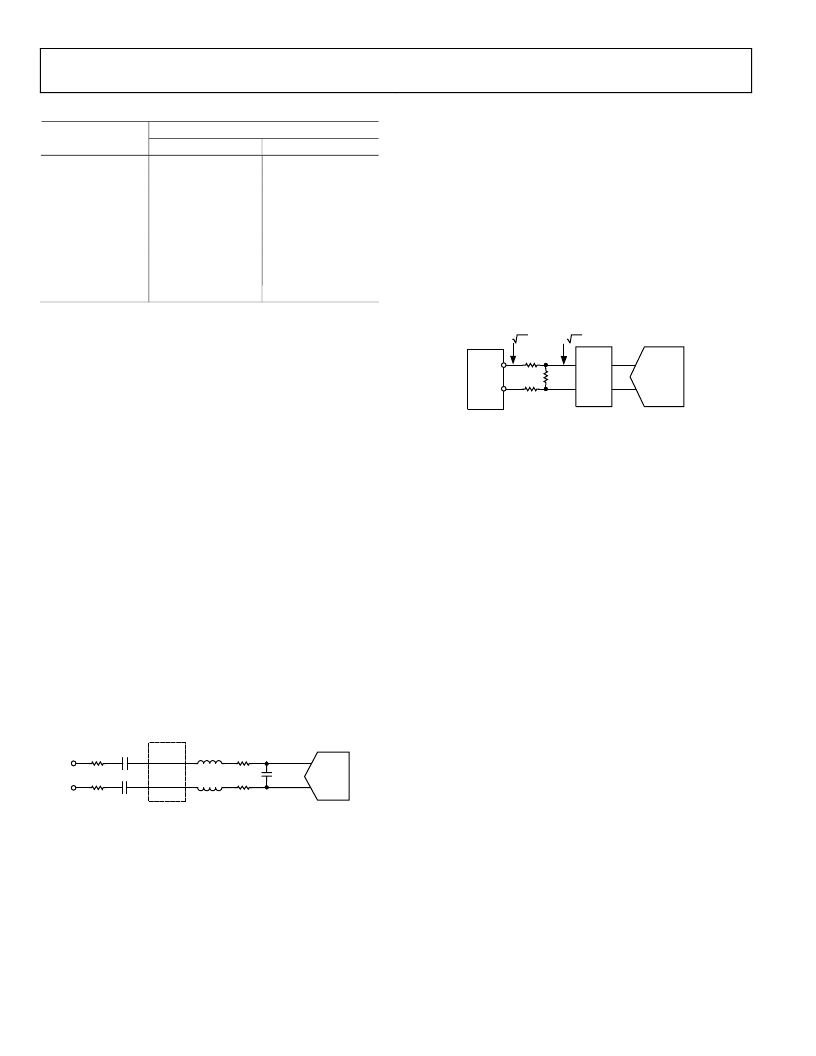

Output Filtering and Series Resistor

Requirements

To ensure stability at the high end of the gain control range,

series resistors or ferrite beads are recommended for the

outputs when driving large capacitive loads, or circuits on other

boards,. These components can be part of the external

noise filter.

Recommended resistor values are 84.5 for LO gain mode and

100 for HI gain mode (see Figure 66) and are placed near

Pins VOH and VOL. Lower value resistors are permissible for

applications with nearby loads or with gains less than 40 dB.

Lower values are best selected empirically.

An antialiasing noise filter is typically used with an ADC. Filter

requirements are application dependent.

When the ADC resides on a separate board, the majority of

filter components should be placed nearby to suppress noise

picked up between boards and mitigates charge kickback from

the ADC inputs. Any series resistance beyond that required for

output stability should be placed on the ADC board. Figure 70

shows a second order low-pass filter with a bandwidth of

20 MHz. The capacitor is chosen in conjunction with the 10 pF

input capacitance of the ADC.

18pF

OPTIONAL

BACKPLANE

84.5

0.1

μ

F

0.1

μ

F

1.5

μ

H

1.5

μ

H

158

158

84.5

ADC

Figure 70. 20 MHz Second-Order Low-Pass Filter

DRIVING ADCS

The output drive will accommodate a wide range of ADCs. The

noise floor requirements of the VGA will depend on a number

of application factors, including bit resolution, sampling rate,

full-scale voltage, and the bandwidth of the noise/antialias filter.

The output noise floor and gain range can be adjusted by

selecting HI or LO gain mode.

The relative noise and distortion performance of the two gain

modes can be compared in Figure 21 and Figure 27 through

Figure 37. The 48 nV/√Hz noise floor of the LO gain mode is

suited to converters with higher sampling rates or resolutions

(such as 12 bits). Both gain modes can accommodate ADC full-

scale voltages as high as 4 V p-p. Since distortion performance

remains favorable for output voltages as high as 4 V p-p (see

Figure 32), it is possible to lower the output-referred noise even

further by using a resistive attenuator (or transformer) at the

output. The circuit in Figure 71 has an output full-scale range of

2 V p-p, a gain range of –10.5 dB to +37.5 dB, and an output

noise floor of 24 nV/√Hz, making it suitable for some 14-bit

ADC applications.

VOH

VOL

LPF

4V p-p DIFF,

48n V/

187

2V p-p DIFF,

24n V/

2:1

374

HZ

187

ADC

AD6644

HZ

0

Figure 71. Adjusting the Noise Floor for 14-Bit ADCs

OVERLOAD

These devices respond gracefully to large signals that overload

its input stage and to normal signals that overload the VGA

when the gain is set unexpectedly high. Each stage is designed

for clean-limited overload waveforms and fast recovery when

gain setting or input amplitude is reduced.

Signals larger than ±275 mV at the LNA input are clipped to

5 V p-p differential prior to the input of the VGA. Figure 44

shows the response to a 1 V p-p input burst. The symmetric

overload waveform is important for applications, such as CW

Doppler ultrasound, where the spectrum of the LNA outputs

during overload is critical. The input stage is also designed to

accommodate signals as high as ±2.5 V without triggering the

slow-settling ESD input protection diodes.

Both stages of the VGA are susceptible to overload. Postamp

limiting is more common and results in the clean-limited

output characteristics found in Figure 45. Under more extreme

conditions, the X-AMP will overload, causing the minor glitches

evident in Figure 46. Recovery is fast in all cases. The graph in

Figure 72 summarizes the combinations of input signal and

gain that lead to the different types of overload.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD8332ACP-REEL | Ultralow Noise VGAs with Preamplifier and Programmable RIN |

| AD8332ACP-REEL7 | Ultralow Noise VGAs with Preamplifier and Programmable RIN |

| AD8332ARU | Ultralow Noise VGAs with Preamplifier and Programmable RIN |

| AD8331ARQ-REEL | Ultralow Noise VGAs with Preamplifier and Programmable RIN |

| AD8331ARQ-REEL7 | Ultralow Noise VGAs with Preamplifier and Programmable RIN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD8332-EVALZ | 功能描述:BOARD EVAL FOR AD8332 RoHS:是 類別:編程器,開發(fā)系統(tǒng) >> 評(píng)估板 - 運(yùn)算放大器 系列:X-AMP® 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- |

| AD8333 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DC to 50 MHz, Dual I/Q Demodulator and Phase Shifter |

| AD8333ACPZ | 制造商:Analog Devices 功能描述:I/Q DEMODULATOR DUAL LFCSP-32 制造商:Analog Devices 功能描述:I/Q, DEMODULATOR, DUAL, LFCSP-32 |

| AD8333ACPZ-REEL | 功能描述:IC DEMODULATOR DUAL I/Q 32LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 解調(diào)器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:- 功能:解調(diào)器 LO 頻率:- RF 頻率:70MHz ~ 300MHz P1dB:-9dBm 增益:- 噪音數(shù)據(jù):6.36dB 電流 - 電源:41.5mA 電源電壓:2.7 V 封裝/外殼:28-WFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:28-TQFN-EP(5x5) 包裝:帶卷 (TR) |

| AD8333ACPZ-REEL7 | 功能描述:IC DEMODULATOR DUAL I/Q 32LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 解調(diào)器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:- 功能:解調(diào)器 LO 頻率:- RF 頻率:70MHz ~ 300MHz P1dB:-9dBm 增益:- 噪音數(shù)據(jù):6.36dB 電流 - 電源:41.5mA 電源電壓:2.7 V 封裝/外殼:28-WFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:28-TQFN-EP(5x5) 包裝:帶卷 (TR) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。