- 您現(xiàn)在的位置:買賣IC網(wǎng) > Datasheet目錄38 > AD652SQ (Analog Devices Inc)IC V-F CONV SYNCH MONO 5V 16CDIP Datasheet資料下載

參數(shù)資料

| 型號: | AD652SQ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 7/28頁 |

| 文件大?。?/td> | 779K |

| 描述: | IC V-F CONV SYNCH MONO 5V 16CDIP |

| 標準包裝: | 1 |

| 類型: | 電壓至頻率 |

| 頻率 - 最大: | 2MHz |

| 全量程: | ±25ppm/°C |

| 線性: | ±0.005% |

| 安裝類型: | 通孔 |

| 封裝/外殼: | 16-CDIP(0.300",7.62mm) |

| 供應(yīng)商設(shè)備封裝: | 16-CDIP |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AD652

Rev. C | Page 7 of 28

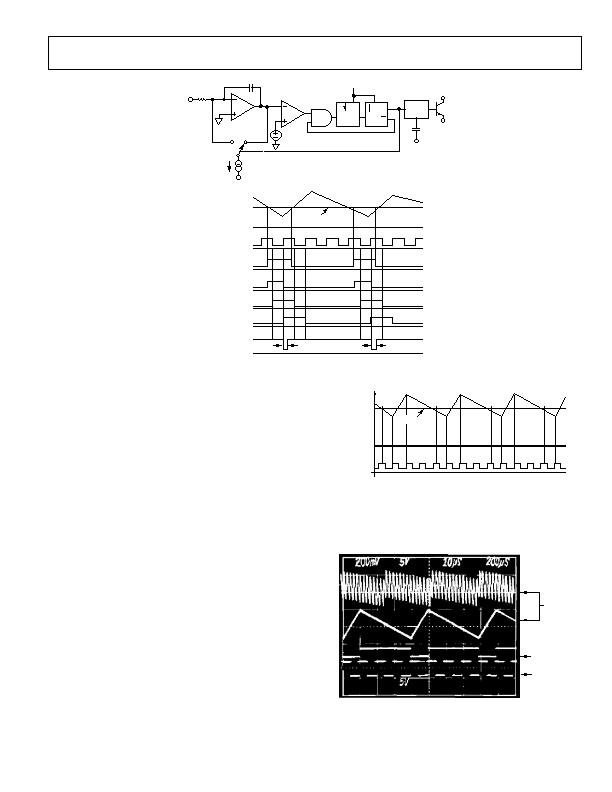

COMPARATOR

AND

CK

Q

D

G

Q

D

Q

D FLOP

LATCH

CLOCK IN

ONE

SHOT

C

OS

5V

C

INT

R

IN

INTEGRATOR

H L

1mA

V

S

V

IN

t

OS

t

OS

INTEGRATOR

OUTPUT

THRESHOLD

CLOCK

COMPARATOR

OUT

AND

OUT

D FLOP

OUT

LATCH

OUT

FREQ

OUT

Figure 4. Block Diagram and System Waveforms

Figure 4 shows that the period between output pulses is

constrained to be an exact multiple of the clock period.

Consider an input current of exactly one quarter the value of

the reference current. In order to achieve a charge balance, the

output frequency equals the clock frequency divided by four:

one clock period for reset and three clock periods of integrate.

This is shown in Figure 5. If the input current is increased by a

very small amount, the output frequency should also increase

by a very small amount. Initially, however, no output change is

observed for a very small increase in the input current. The

output frequency continues to run at one quarter of the clock,

delivering an average of 250 礎(chǔ) to the summing junction. Since

the input current is slightly larger than this, charge accumulates

in the integrator and the sawtooth signal starts to drift down-

ward. As the integrator sawtooth drifts down, the comparator

threshold is crossed earlier and earlier in each successive cycle,

until finally, a whole cycle is lost. When the cycle is lost, the

integrate phase lasts for two periods of the clock instead of the

usual three periods. Thus, among a long string of divide-by-

fours, an occasional divide-by-three occurs; the average of the

output frequency is very close to one quarter of the clock, but

the instantaneous frequency can be very different.

INTEGRATO

OUT

CLOCK

THRESHOLD

Figure 5. Integrator Output for I

IN

= 250 礎(chǔ)

Because of this, it is very difficult to observe the waveform on

an oscilloscope. During all of this time, the signal at the output

of the integrator is a sawtooth wave with an envelope that is also

a sawtooth. See Figure 6.

200?/SPAN>s/BOX

100?/SPAN>s/BOX

C

INT

FREQ OUT

10?/SPAN>s/BOX

CLOCK IN

10?/SPAN>s/BOX

Figure 6. Integrator Output for I

IN

Slightly Greater than 250 祍

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD654JNZ/+ | IC CONV VOLT-FREQ 500KHZ 8DIP |

| AD7740YRM | IC CONVERTER V TO FREQ 8-MSOP |

| ADM1070ARTZ-REEL7 | IC CTRLR HOTSWAP -48V SOT23-6 |

| ADM1073ARU-REEL | IC CTRLR HOTSWAP -48V 14TSSOP |

| ADM4210-2AUJZ-RL7 | IC CTLR HOTSWAP LV TSOT23-6 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD652SQ/883B | 功能描述:電壓頻率轉(zhuǎn)換及頻率電壓轉(zhuǎn)換 IC - SYNC V/F CONVERTER RoHS:否 制造商:Texas Instruments 全標度頻率:4000 KHz 線性誤差:+/- 1 % FSR 電源電壓-最大: 電源電壓-最小: 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-14 封裝:Tube |

| AD652SQ/883B2 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Monolithic Synchronous Voltage-to-Frequency Converter |

| AD652SQ2 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Monolithic Synchronous Voltage-to-Frequency Converter |

| AD652SQ883B2 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Monolithic Synchronous Voltage-to-Frequency Converter |

| AD652SW | 制造商:AD 制造商全稱:Analog Devices 功能描述:Monolithic Synchronous Voltage-to-Frequency Converter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。