- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375230 > AD1981BLJSTZ2 (Analog Devices, Inc.) AC ’97 SoundMAX㈢ Codec PDF資料下載

參數(shù)資料

| 型號(hào): | AD1981BLJSTZ2 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | Codec |

| 英文描述: | AC ’97 SoundMAX㈢ Codec |

| 中文描述: | ㈢交流\u0026#39;97 SoundMAX編解碼器 |

| 文件頁(yè)數(shù): | 21/28頁(yè) |

| 文件大小: | 215K |

| 代理商: | AD1981BLJSTZ2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

REV. 0

AD1981BL

–21–

PRO

Professional. 1 indicates professional use of channel status.

0 indicates consumer.

AUD

Non-Audio. 1 indicates data is non-PCM format.

0 data is PCM.

COPY

Copyright. 1 indicates copyright is asserted.

0 copyright is not asserted.

Pre-Emphasis. 1 indicates filter pre-emphasis is 50

μ

s/15

μ

s.

0 pre-emphasis is none.

PRE

CC[6:0]

Category Code. Programmed according to IEC standards, or as appropriate.

L

Generation Level. Programmed according to IEC standards, or as appropriate.

SPSR[1:0]

SPDIF Transmit Sample Rate.

SPSR[1:0] = 00 Transmit sample rate = 44.1 kHz.

SPSR[1:0] = 01 Reserved.

SPSR[1:0] = 10 Transmit sample rate = 48 kHz (reset default).

SPSR[1:0] = 11 Not supported.

V

Validity. This bit affects the validity flag (Bit 28 transmitted in each SPDIF L/R subframe) and enables the

SPDIF transmitter to maintain connection during error or mute conditions.

V = 1 Each SPDIF subframe (L + R) has Bit 28 set to 1. This tags both samples as invalid.

V = 0 Each SPDIF subframe (L + R) has Bit 28 set to 0 for valid data and 1 for invalid data (error condition).

Note that when V = 0, asserting the VFORCE bit (D15) in Register 2Ah (Ext’d Audio Stat/Ctrl) will force the

Validity flag low, marking both samples as valid.

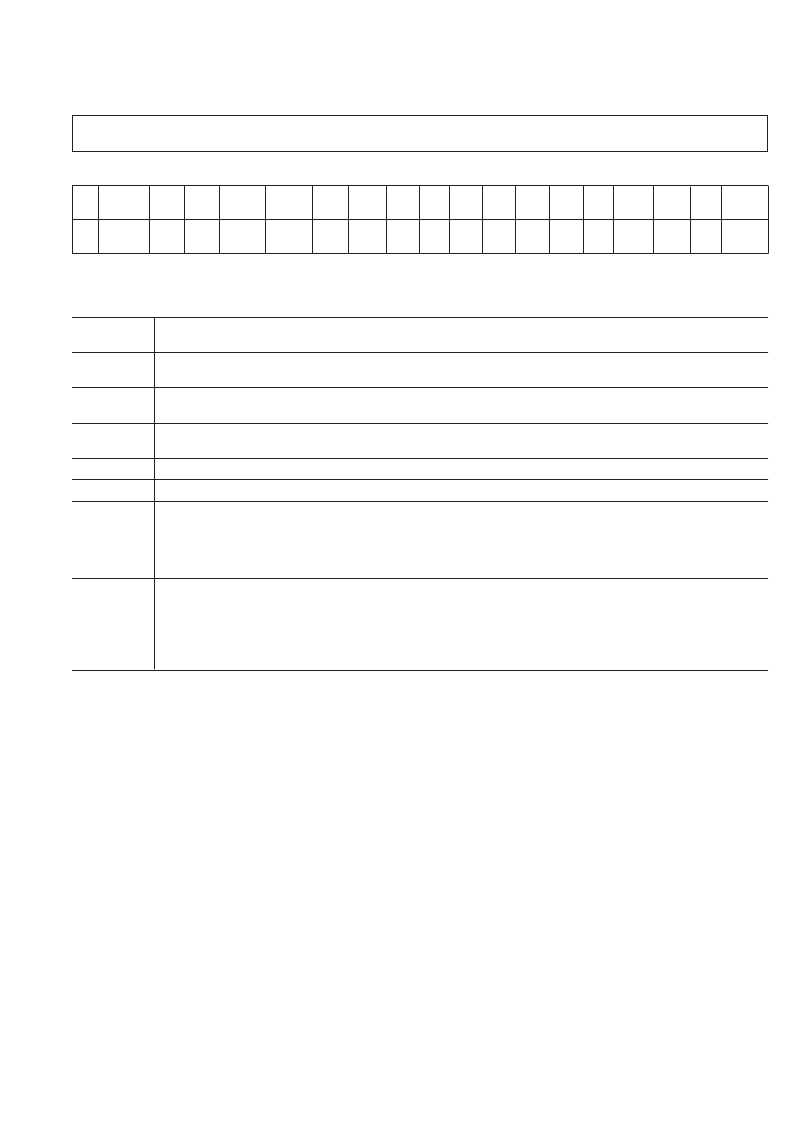

SPDIF Control Register (Index 3Ah)

Reg

No.

Name

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Default

3Ah SPDIF

Control

V

X

SPSR1

SPSR0

L

CC6

CC5

CC4

CC3

CC2

CC1

CC0

PRE

COPY

AUD

PRO

2000h

Register 3Ah is a read/write register that controls SPDIF functionality and manages bit fields propagated as channel status (or subframe in the V case). With the

exception of V, this register should be written to only when the SPDIF transmitter is disabled (SPDIF bit in Register 2Ah is 0). This ensures that control and status

information start up correctly at the beginning of SPDIF transmission.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1981BLJSTZ-REEL2 | AC ’97 SoundMAX㈢ Codec |

| AD1981HD | HD Audio SoundMAX Codec |

| AD1981HDJSTZ | HD Audio SoundMAX Codec |

| AD1981HDJSTZ-REEL | HD Audio SoundMAX Codec |

| AD1983 | HD Audio SoundMAX Codec |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD1981BLJSTZ-REEL | 制造商:Analog Devices 功能描述:Audio Codec 4ADC / 2DAC 20-Bit 48-Pin LQFP T/R |

| AD1981BLJSTZ-REEL2 | 制造商:AD 制造商全稱:Analog Devices 功能描述:AC ’97 SoundMAX㈢ Codec |

| AD1981BWBSTZ | 制造商:Analog Devices 功能描述: |

| AD1981BWBSTZ-REEL | 制造商:Analog Devices 功能描述:ANAAD1981BWBSTZ-REEL AC'97 SOUNDMAX CODE |

| AD1981HD | 制造商:AD 制造商全稱:Analog Devices 功能描述:HD Audio SoundMAX Codec |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。