- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375230 > AD1981BLJSTZ2 (Analog Devices, Inc.) AC ’97 SoundMAX㈢ Codec PDF資料下載

參數(shù)資料

| 型號: | AD1981BLJSTZ2 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | Codec |

| 英文描述: | AC ’97 SoundMAX㈢ Codec |

| 中文描述: | ㈢交流\u0026#39;97 SoundMAX編解碼器 |

| 文件頁數(shù): | 17/28頁 |

| 文件大小: | 215K |

| 代理商: | AD1981BLJSTZ2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

REV. 0

AD1981BL

–17–

ADC

ADC Sections Ready to Transmit Data.

DAC

DAC Sections Ready to Accept Data.

ANL

Analog Amplifiers, Attenuators, and Mixers Ready.

REF

Voltage References, V

REF

and V

REFOUT

up to Nominal Level.

Codec Power-Down Modes. The first three bits are to be used individually rather than in combination with each

other. PR3 can be used in combination with PR2 or by itself. The mixer and reference cannot be powered down via

PR3 unless the ADCs and DACs are also powered down.

Nothing else can be powered up until the reference is up. PR5 has no effect unless all ADCs, DACs, and the ac-link

are powered down. The reference and the mixer can be either up or down, but all power-up sequences must be

allowed to run to completion before PR5 and PR4 are both set.

In multiple codec systems, the master codec’s PR5 and PR4 bits control the slave codec. PR5 is also effective in the

slave codec if the master’s PR5 bit is clear, but the PR4 bit has no effect except to enable or disable PR5.

PR [6:0]

EAPD

External Audio Power-Down Control. Controls the state of the EAPD pin.

EAPD = 0 sets the EAPD pin low, enabling an external power amplifier (reset default).

EAPD = 1 sets the EAPD pin high, shutting the external power amplifier off.

Power-Down State

Set Bits

PR [6:0]

ADCs and Input Mux Power-Down

PR0

[000 0001]

DACs Power-Down

PR1

[000 0010]

Analog Mixer Power-Down (V

REF

and V

REFOUT

On)

Analog Mixer Power-Down (V

REF

and V

REFOUT

Off)

AC-Link Interface Power-Down

PR1, PR2

[000 0101]

PR0, PR1, PR3

[000 1011]

PR4

[001 0000]

Internal Clocks Disabled

PR0, PR1, PR4, PR5

[011 0011]

ADC and DAC Power-Down

PR0, PR1

[000 0011]

V

REF

Standby Mode

Total Power-Down

PR0, PR1, PR2, PR4, PR5

[011 0111]

PR0, PR1, PR2, PR3, PR4, PR5, PR6

[111 1111]

Headphone Amp Power-In Standby

PR6

[100 0000]

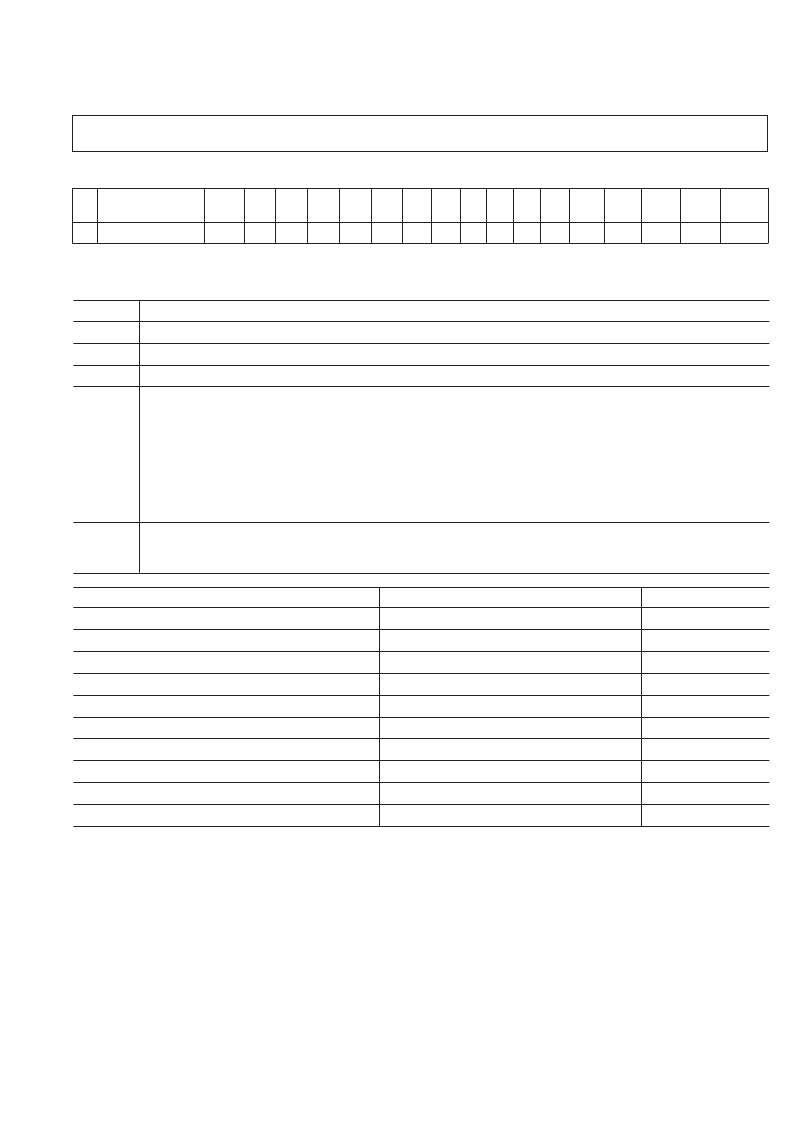

Power-Down Control/Status Register (Index 26h)

Reg

No. Name

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Default

26h Power-Down Ctrl/Stat

EAPD

PR6

PR5

PR4

PR3

PR2

PR1

PR0

X

X

X

X

REF

ANL

DAC

ADC

000Xh

The ready bits are read-only; writing to REF, ANL, DAC, ADC will have no effect. These bits indicate the status for the AD1981BL subsections. If the bit is a 1, that

subsection is

ready

.

Ready

is defined as the subsection able to perform in its nominal state. All registers not shown, and bits containing an X are assumed to be reserved.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1981BLJSTZ-REEL2 | AC ’97 SoundMAX㈢ Codec |

| AD1981HD | HD Audio SoundMAX Codec |

| AD1981HDJSTZ | HD Audio SoundMAX Codec |

| AD1981HDJSTZ-REEL | HD Audio SoundMAX Codec |

| AD1983 | HD Audio SoundMAX Codec |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD1981BLJSTZ-REEL | 制造商:Analog Devices 功能描述:Audio Codec 4ADC / 2DAC 20-Bit 48-Pin LQFP T/R |

| AD1981BLJSTZ-REEL2 | 制造商:AD 制造商全稱:Analog Devices 功能描述:AC ’97 SoundMAX㈢ Codec |

| AD1981BWBSTZ | 制造商:Analog Devices 功能描述: |

| AD1981BWBSTZ-REEL | 制造商:Analog Devices 功能描述:ANAAD1981BWBSTZ-REEL AC'97 SOUNDMAX CODE |

| AD1981HD | 制造商:AD 制造商全稱:Analog Devices 功能描述:HD Audio SoundMAX Codec |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。