- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375227 > ACD2204S&P1 (ANADIGICS, Inc.) CATV/TV/Video Downconverter with Dual Synthesizer PDF資料下載

參數(shù)資料

| 型號: | ACD2204S&P1 |

| 廠商: | ANADIGICS, Inc. |

| 英文描述: | CATV/TV/Video Downconverter with Dual Synthesizer |

| 中文描述: | 有線電視/電視/視頻變頻器雙合成 |

| 文件頁數(shù): | 11/20頁 |

| 文件大小: | 350K |

| 代理商: | ACD2204S&P1 |

PRELIMINARY DATA SHEET - Rev 1.0

04/2003

11

ACD2204

2

2

1

2

0

2

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

1

9

8

7

6

5

4

3

2

1

e

d

o

M

m

a

r

g

o

r

P

r

e

n

u

o

C

R

r

e

d

D

e

c

n

e

r

e

R

t

e

S

D

5

D

4

D

3

D

2

D

1

R

1

5

R

1

4

R

1

3

R

1

2

R

1

1

R

1

0

R

9

R

8

R

7

R

6

R

5

R

4

R

3

R

2

R

1

S

2

S

1

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

0

2

2

1

2

0

2

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

1

9

8

7

6

5

4

3

2

1

m

e

a

r

d

g

o

o

r

M

P

r

e

n

u

o

C

B

r

e

d

D

n

M

r

e

n

u

o

C

A

r

e

d

D

n

M

t

e

S

C

2

C

1

B

1

1

B

1

0

B

9

B

8

B

7

B

6

B

5

B

4

B

3

B

2

B

1

A

7

A

6

A

5

A

4

A

3

A

2

A

1

S

2

S

1

0

0

0

0

1

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

1

1

0

0

0

1

1

0

0

0

1

1

0

0

1

1

LSB

MSB

LSB

MSB

For the up converter, the 4 MHz crystal oscillator frequency and the 250 KHz phase detector comparison

frequency are used to yield R

PLL1

= 4 MHz / 250 KHz = 16, and so the bit values for the up converter R counter

are R

PLL1

= 000000000010000.

Calculation of Main Divider Values

The values for the A and B counters are determined by the desired VCO output frequency for the local

oscillator and the phase detector comparison frequency:

N = f

VCO

/ f

PD

B = trunc(N / P)

A = N - (B x P)

The down converter local oscillator frequency will be 1087.75 MHz - 45.75 MHz = 1042 MHz in this example.

The main divider ratio for the down converter, then, is N

PLL2

= 1042 MHz / 62.5 KHz = 16672. Since P = 64 in the

ACD2204, B

PLL2

= trunc(16672 / 64) = 260, and A

PLL2

= 16672 - (260 x 64) = 32. These results give bit values

of B

PLL2

= 00100000100 and A

PLL2

= 0100000 for the B and A counters.

The up converter local oscillator frequency will be 499.25 MHz + 1087.75 MHz = 1587 MHz in this example.

Therefore, N

PLL1

= 1587 MHz / 250 KHz = 6348, B

PLL1

= trunc(6348 / 64) = 99, and A

PLL1

= 6348 - (99 x 64) = 12.

These results give bit values of B

PLL1

= 00001100011 and A

PLL1

= 0001100 for the B and A counters.

Phase Detector Polarity

Assuming the VCO for the up converter has a negative slope, the phase detector polarity for PLL1 should be

negative, and D1

PLL1

= 1. If the VCO for the down converter has a positive slope, the phase detector polarity for

PLL2 should be positive, and D1

PLL2

= 0.

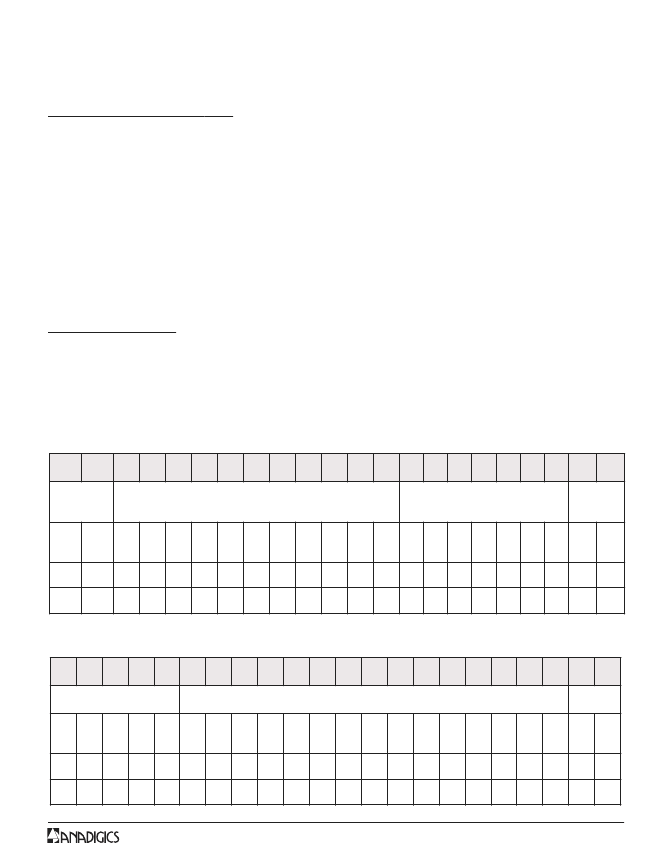

In summary, for this example, the four register programming words are shown in Tables 16 and 17:

Table 16: PLL1 and PLL2 Reference Divider Register Bits

for Synthesizer Programming Example

Table 17: PLL1 and PLL2 Main Divider Register Bits

for Synthesizer Programming Example

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACD2206 | ER 37C 37#16 PIN PLUG |

| ACF2101 | Low Noise, Dual SWITCHED INTEGRATOR |

| ACF2101BP | Low Noise, Dual SWITCHED INTEGRATOR |

| ACF2101BU | Low Noise, Dual SWITCHED INTEGRATOR |

| ACH16373DGG | JT 6C 6#12 PIN PLUG |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACD2206 | 制造商:ANADIGICS 制造商全稱:ANADIGICS, Inc 功能描述:CATV/TV/VIDEO DOWNCONVERTER WITH DUAL SYNTHESIZER |

| ACD2206RS8P1 | 制造商:ANADIGICS Inc 功能描述:DOWNCONVERTER |

| ACD2206S8P1 | |

| ACD221RNM | 制造商:Eaton Corporation 功能描述:30A/2P Fusible Non-Metallic AC Disconnect 240V Nema 3R |

| ACD222URNM | 制造商:Eaton Corporation 功能描述:60A/2P Non-Fusible Non-Metallic AC Disconnect 240V Nema 3R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。