- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375141 > A43P26161V-95F (AMIC Technology Corporation) 1M X 16 Bit X 4 Banks Low Power Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | A43P26161V-95F |

| 廠商: | AMIC Technology Corporation |

| 英文描述: | 1M X 16 Bit X 4 Banks Low Power Synchronous DRAM |

| 中文描述: | 100萬× 16位× 4個(gè)銀行的低功耗同步DRAM |

| 文件頁數(shù): | 11/44頁 |

| 文件大小: | 1122K |

| 代理商: | A43P26161V-95F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

A43P26161

PRELIMINARY

(July, 2005, Version 1.1)

10

AMIC Technology, Corp.

Power Up Sequence

1. Apply power and start clock, Attempt to maintain CKE = “H”, DQM = “H” and the other pins are NOP condition at inputs.

2. Maintain stable power, stable clock and NOP input condition for a minimum of 200

μ

s.

3. Issue precharge commands for all banks of the devices.

4. Issue 2 or more auto-refresh commands.

5. Issue a mode register set command to initialize the mode register. The device is now ready for normal operation.

6. Issue a extended mode register set command to define DS or PASR operating type of the device after normal MRS.

cf.) Sequence of 4 & 5 may be changed.

EMRS cycle is not mandatory and the EMRS command needs to be issued only when DS or PASR is used.

The default state without EMRS command issued is the half driver strength and full array refreshed.

The device is now ready for the operation selected by EMRS.

For operating with DS or PASR, set DS or PASR mode in EMRS setting stage.

In order to adjust another mode in the state of DS or PASR mode, additional EMRS set is required but power up sequence is not

needed again at this time. In that case, all banks have to be in idle state prior to adjusting EMRS set.

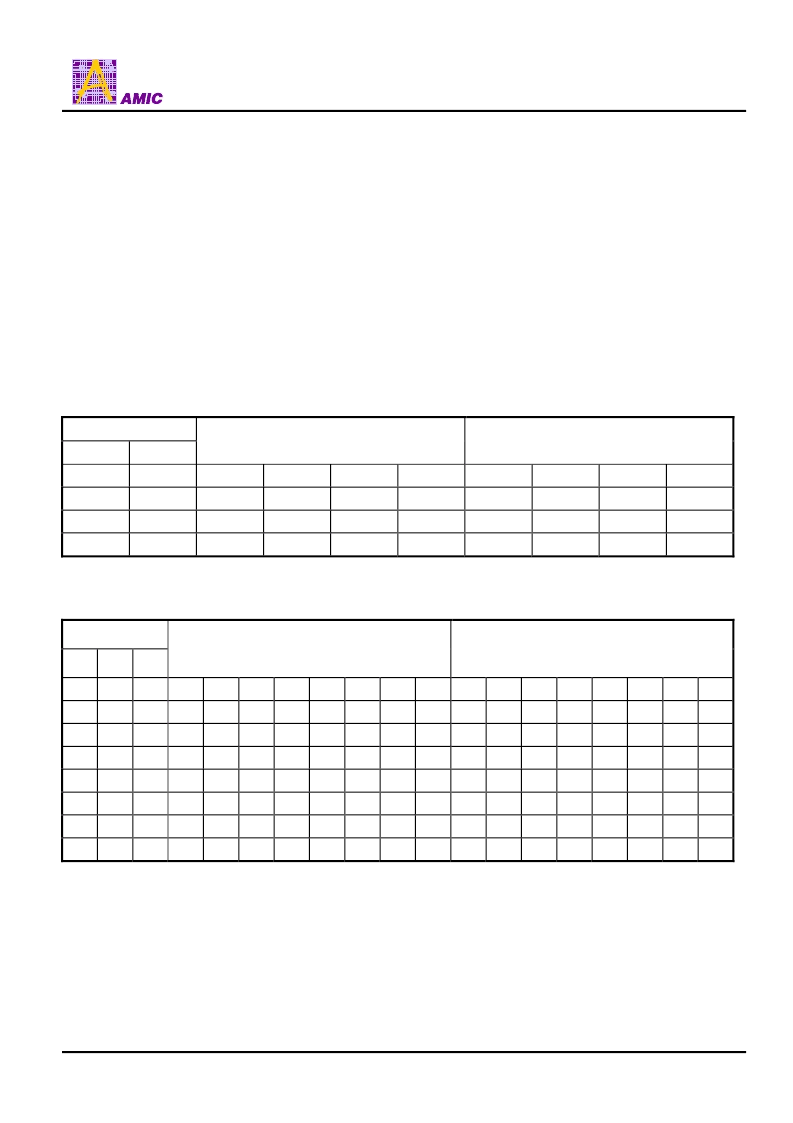

Burst Sequence (Burst Length = 4)

Initial address

A1

A0

Sequential

Interleave

0

0

0

1

2

3

0

1

2

3

0

1

1

2

3

0

1

0

3

2

1

0

2

3

0

1

2

3

0

1

1

1

3

0

1

2

3

2

1

0

Burst Sequence (Burst Length = 8)

Initial address

A2

A1

A0

Sequential

Interleave

0

0

0

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

0

1

1

2

3

4

5

6

7

0

1

0

3

2

5

4

7

6

0

1

0

2

3

4

5

6

7

0

1

2

3

0

1

6

7

4

5

0

1

1

3

4

5

6

7

0

1

2

3

2

1

0

7

6

5

4

1

0

0

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

1

0

1

5

6

7

0

1

2

3

4

5

4

7

6

1

0

3

2

1

1

0

6

7

0

1

2

3

4

5

6

7

4

5

2

3

0

1

1

1

1

7

0

1

2

3

4

5

6

7

6

5

4

3

2

1

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A43P26161V-95U | 1M X 16 Bit X 4 Banks Low Power Synchronous DRAM |

| A43P26161G-75F | OSC 3.3V SMT 7X5 CMOS |

| A43P26161G-75U | 1M X 16 Bit X 4 Banks Low Power Synchronous DRAM |

| A43P26161G-75UF | 1M X 16 Bit X 4 Banks Low Power Synchronous DRAM |

| A43P26161G-95 | 1M X 16 Bit X 4 Banks Low Power Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A43P26161V-95U | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:1M X 16 Bit X 4 Banks Low Power Synchronous DRAM |

| A43P26161V-95UF | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:1M X 16 Bit X 4 Banks Low Power Synchronous DRAM |

| A43P2616G-75I | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:1M X 16 Bit X 4 Banks Synchronous DRAM |

| A43P2616G-95I | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:1M X 16 Bit X 4 Banks Synchronous DRAM |

| A43P2616V-75I | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:1M X 16 Bit X 4 Banks Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。