- 您現(xiàn)在的位置:買賣IC網 > PDF目錄375141 > A43L8316AV-5 (AMIC Technology Corporation) 128K X 16 Bit X 2 Banks Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | A43L8316AV-5 |

| 廠商: | AMIC Technology Corporation |

| 英文描述: | 128K X 16 Bit X 2 Banks Synchronous DRAM |

| 中文描述: | 128K的× 16位× 2銀行同步DRAM |

| 文件頁數(shù): | 6/45頁 |

| 文件大?。?/td> | 1008K |

| 代理商: | A43L8316AV-5 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

A43L8316A

(September, 2003, Version 1.0)

5

AMIC Technology, Corp.

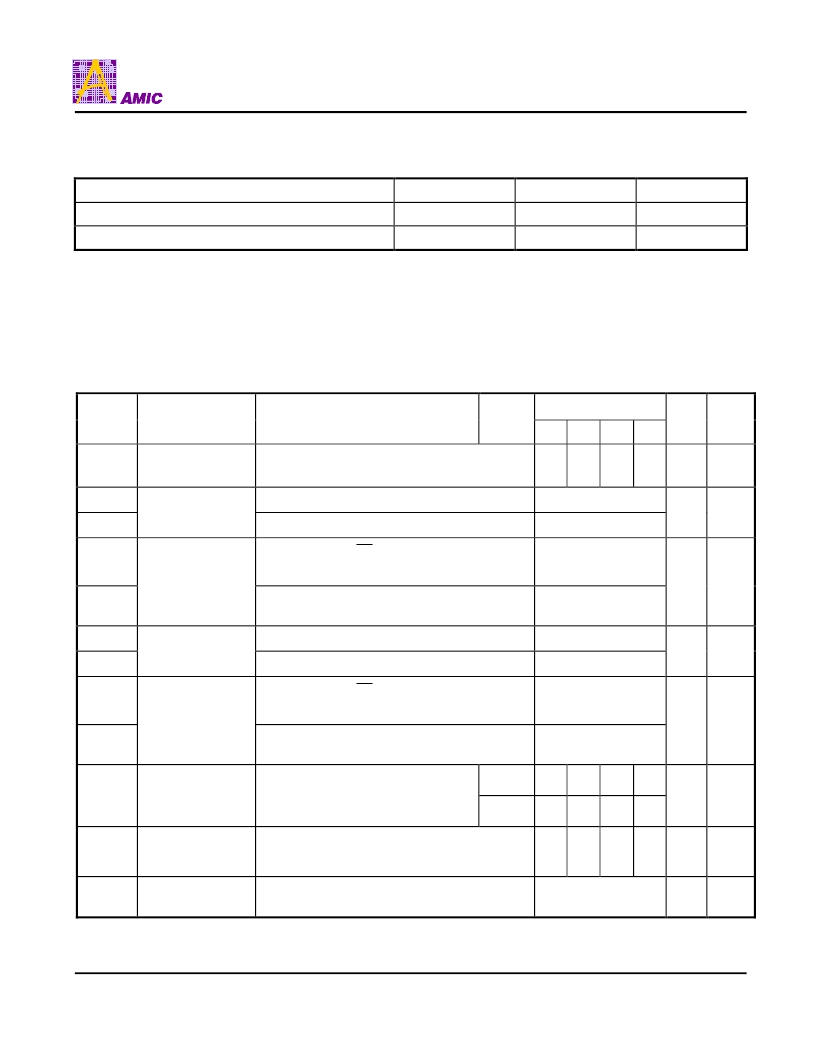

Decoupling Capacitance Guide Line

Recommended decoupling capacitance added to power line at board.

Parameter

Symbol

Value

Unit

Decoupling Capacitance between VDD and VSS

C

DC1

0.1 + 0.01

μ

F

Decoupling Capacitance between VDDQ and VSSQ

C

DC2

0.1 + 0.01

μ

F

Note:

1. VDD and VDDQ pins are separated each other.

All VDD pins are connected in chip. All VDDQ pins are connected in chip.

2. VSS and VSSQ pins are separated each other

All VSS pins are connected in chip. All VSSQ pins are connected in chip.

DC Electrical Characteristics

(Recommended operating condition unless otherwise noted, T

A

= 0 to 70

°

C)

Speed

Symbol

Parameter

Test Conditions

CAS

Latency

-5

-5.5

-6

-7

Unit

Notes

I

cc1

Operating Current

(One Bank Active)

Burst Length = 1

t

RC

≥

t

RC

(min), t

CC

≥

t

CC

(min

)

, I

OL

= 0mA

230

210

190

160

mA

1

I

cc2

P

CKE

≤

V

IL

(max), t

CC

= 15ns

1

I

cc2

PS

Precharge Standby

Current in power-

down mode

CKL

≤

VIL(max), t

CC

=

∞

1

mA

I

CC2

N

CKE

≥

V

IH

(min), CS

≥

V

IH

(min), t

CC

= 15ns

Input signals are changed one time during 30ns

15

I

CC2

NS

Precharge Standby

Current in non

power-down mode

CKE

≥

V

IH

(min), CLK

≤

V

IL

(max), t

CC

=

∞

Input signals are stable.

4

mA

I

CC3

P

CKE

≤

V

IL

(max), t

CC

= 15ns

2

I

CC3

PS

Active Standby

Current in power-

down mode

CKE

≤

V

IL

(max) t

CC

=

∞

1

mA

I

CC3

N

CKE

≥

V

IH

(min), CS

≥

V

IH

(min), t

CC

= 15ns

Input signals are changed one time during 30ns

25

I

CC3

NS

Active Standby

current in non

power-down mode

(One Bank Active)

CKE

≥

V

IH

(min), CLK

≤

V

IL

(max), t

CC

=

∞

Input signals are stable.

15

mA

3

250

230

210

180

I

CC4

Operating Current

(Burst Mode)

I

OL

= 0mA, Page Burst

All bank Activated, t

CCD

= t

CCD

(min)

2

-

-

-

180

mA

1

I

CC5

Refresh Current

t

RC

≥

t

RC

(min)

250

230

210

180

mA

2

I

CC6

Self Refresh

Current

CKE

≤

0.2V

1

mA

Note:

1. Measured with outputs open. Addresses are changed only one time during t

CC

(min).

2. Refresh period is 32ms. Addresses are changed only one time during t

CC

(min).

相關PDF資料 |

PDF描述 |

|---|---|

| A43L8316AV-5.5 | 128K X 16 Bit X 2 Banks Synchronous DRAM |

| A43L8316AV-6 | 128K X 16 Bit X 2 Banks Synchronous DRAM |

| A43L8316AV-7 | 128K X 16 Bit X 2 Banks Synchronous DRAM |

| A43L8316A | 128K X 16 Bit X 2 Banks Synchronous DRAM |

| A43L8316AV | 128K X 16 Bit X 2 Banks Synchronous DRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| A43L8316AV-5.5 | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:128K X 16 Bit X 2 Banks Synchronous DRAM |

| A43L8316AV-6 | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:128K X 16 Bit X 2 Banks Synchronous DRAM |

| A43L8316AV-7 | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:128K X 16 Bit X 2 Banks Synchronous DRAM |

| A43L8316G-75I | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:1M X 16 Bit X 4 Banks Synchronous DRAM |

| A43L8316G-95I | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:1M X 16 Bit X 4 Banks Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。