- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4333 > A14100A-1RQ208I (Microsemi SoC)IC FPGA 10K GATES 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | A14100A-1RQ208I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 86/90頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 10K GATES 208-PQFP |

| 標準包裝: | 24 |

| 系列: | ACT™ 3 |

| LAB/CLB數(shù): | 1377 |

| 輸入/輸出數(shù): | 175 |

| 門數(shù): | 10000 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP 裸露焊盤 |

| 供應商設備封裝: | 208-RQFP(28x28) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁當前第86頁第87頁第88頁第89頁第90頁

R e visio n 3

4 -1

4 – Datasheet Information

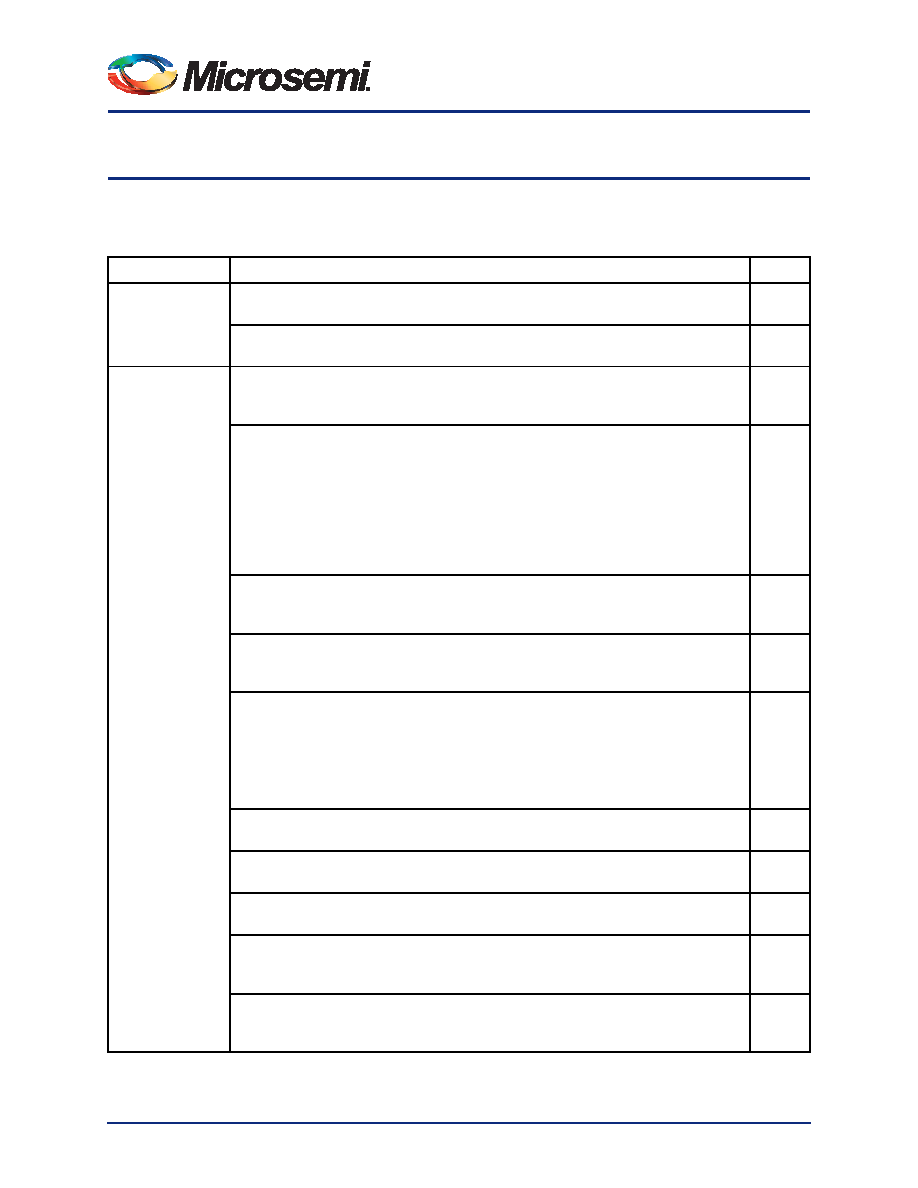

List of Changes

The following table lists critical changes that were made in each version of the datasheet.

Revision

Changes

Page

Revision 3

(January 2012)

The description for SDO pins had earlier been removed from the datasheet and has

now been included again, in the "Pin Descriptions" section (SAR 35820).

SDO pin numbers had earlier been removed from package pin assignment tables in

the datasheet, and have now been restored to the pin tables (SAR 35820).

Revision 2

(September 2011)

The ACT 3 datasheet was formatted newly in the style used for current datasheets.

The same information is present (other than noted in the list of changes for this

revision) but divided into chapters.

N/A

The datasheet was revised to note in multiple places that speed grades –2 and –3

have been discontinued. The following device/package combinations have been

discontinued for all speed grades and temperatures (SAR 33872):

A1415 PG100

A1425 PG133

A1440 PG175

A1460 BG225

I and

others

The "Features" section was revised to state the clock-to-ouput time and on-chip

performance for –1 speed grade as 9.0 ns and 186 MHz. The "General Description"

section was revised in accordance (SAR 33872).

The maximum performance values were updated in Table 1 ACT 3 Family Product

Information, and now reflect worst-case commercial for the –1 speed grade (SAR

33872).

The "Product Plan" table was updated as follows to conform to current offerings (SAR

33872):

The A1415A device is offered in PL84, PG100, and VQ100 packages for Military

application.

The A1440A device is offered in TQ176 and VQ100 packages for Industrial

application.

Table 1-1 Chip-to-Chip Performance (worst-case commercial) was updated to

include data for all speed grades instead of only –3 (SAR 33872).

revised to reflect values for the –1 speed grade (SAR 33872).

Figure 2-10 Timing Model was updated to show data for the –1 speed grade instead

of –3 (SAR 33872).

Conditions was updated to include data for all speed grades instead of only –3 (SAR

33872).

Package names used in the "Package Pin Assignments" section and throughout the

document were revised to match standards given in Package Mechanical Drawings

(SAR 27395).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ASC49DREI-S734 | CONN EDGECARD 98POS .100 EYELET |

| RBB106DHBT-S621 | EDGECARD 212POS DIP R/A .050 SLD |

| ASC50DRTF-S13 | CONN EDGECARD 100POS .100 EXTEND |

| AMC50DRTF-S13 | CONN EDGECARD 100POS .100 EXTEND |

| ASC50DREF-S13 | CONN EDGECARD 100POS .100 EXTEND |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A14100A-2BG313C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A14100A-2BG313I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A14100A-2PG257C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A14100A-2RQ208C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A14100A-2RQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復。