- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36337 > 935237460112 (NXP SEMICONDUCTORS) HORIZ/VERT DEFLECTION IC, PDIP32 PDF資料下載

參數(shù)資料

| 型號: | 935237460112 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 偏轉(zhuǎn) |

| 英文描述: | HORIZ/VERT DEFLECTION IC, PDIP32 |

| 封裝: | PLASTIC, SDIP-32 |

| 文件頁數(shù): | 9/63頁 |

| 文件大?。?/td> | 318K |

| 代理商: | 935237460112 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

1999 Jul 13

17

Philips Semiconductors

Product specication

I2C-bus autosync deection controllers for

PC/TV monitors

TDA4853; TDA4854

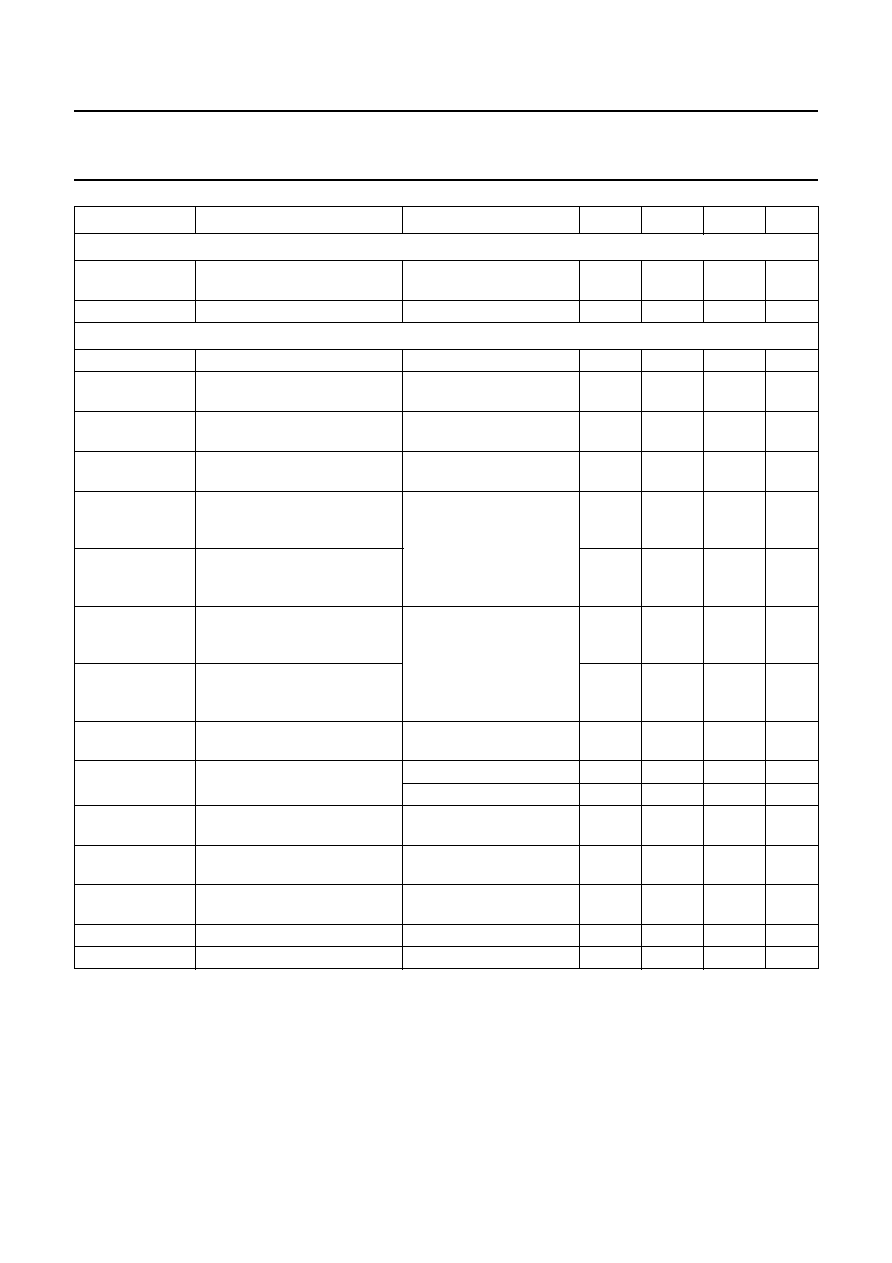

Automatic polarity correction for vertical sync

tW(VSYNC)(max)

maximum width of vertical sync

pulse

400

s

td(VPOL)

delay time for changing polarity

0.45

1.8

ms

Video clamping/vertical blanking output: pin CLBL

tclamp(CLBL)

width of video clamping pulse

measured at VCLBL = 3 V

0.6

0.7

0.8

s

Vclamp(CLBL)

top voltage level of video

clamping pulse

4.32

4.75

5.23

V

TCclamp

temperature coefcient of

Vclamp(CLBL)

4

mV/K

STPSclamp

steepness of slopes for

clamping pulse

RL =1M; CL =20pF

50

ns/V

td(HSYNCt-CLBL)

delay between trailing edge of

horizontal sync and start of

video clamping pulse

clamping pulse triggered

on trailing edge of

horizontal sync;

control bit CLAMP = 0;

measured at VCLBL =3V

130

ns

tclamp1(max)

maximum duration of video

clamping pulse referenced to

end of horizontal sync

1.0

s

td(HSYNCl-CLBL)

delay between leading edge of

horizontal sync and start of

video clamping pulse

clamping pulse triggered

on leading edge of

horizontal sync;

control bit CLAMP = 1;

measured at VCLBL =3V

300

ns

tclamp2(max)

maximum duration of video

clamping pulse referenced to

end of horizontal sync

0.15

s

Vblank(CLBL)

top voltage level of vertical

blanking pulse

notes 1 and 2

1.7

1.9

2.1

V

tblank(CLBL)

width of vertical blanking pulse

at pins CLBL and HUNLOCK

control bit VBLK = 0

220

260

300

s

control bit VBLK = 1

305

350

395

s

TCblank

temperature coefcient of

Vblank(CLBL)

2

mV/K

Vscan(CLBL)

output voltage during vertical

scan

ICLBL = 0

0.59

0.63

0.67

V

TCscan

temperature coefcient of

Vscan(CLBL)

2

mV/K

Isink(CLBL)

internal sink current

2.4

mA

IL(CLBL)

external load current

3.0

mA

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935260802112 | HORIZ/VERT DEFLECTION IC, PDIP32 |

| 935260845118 | PLL FREQUENCY SYNTHESIZER, 2200 MHz, PDSO16 |

| 935260845112 | PLL FREQUENCY SYNTHESIZER, 2200 MHz, PDSO16 |

| 935260937112 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935260937118 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935241-0001 | 制造商: 功能描述: 制造商:DIGITRAN 功能描述: 制造商:undefined 功能描述: |

| 935241-1 | 制造商:DIGITRAN 功能描述: 制造商:DTRAN 功能描述: |

| 935245650125 | 制造商:NXP Semiconductors 功能描述:Inverter 1-Element CMOS 5-Pin TSSOP T/R |

| 935248-90 | 制造商:JANCO 功能描述:935248-90 |

| 9-3525-012 | 制造商:KEYSTONE 功能描述:MODIFIED 3525,VERSION E |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。