- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24634 > 932S208DFT (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號: | 932S208DFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | GREEN, MO-118, SSOP-56 |

| 文件頁數(shù): | 7/22頁 |

| 文件大小: | 231K |

| 代理商: | 932S208DFT |

15

Integrated

Circuit

Systems, Inc.

ICS932S208

0743D—07/07/04

The PCI_STOP# signal is on an active low input controlling PCI and SRC outputs. If PCIF (2:0) and SRC clocks can be set to

be free-running through I2C programming. Outputs set to be free-running will ignore both the PCI_STOP pin and the

PCI_STOP register bit.

PCI Stop Functionality

#

P

O

T

S

_

I

C

PU

P

C#

U

P

CC

R

S#

C

R

S6

6

V

3I

C

P

/

F

I

C

PT

O

D

/

B

S

UF

E

Re

t

o

N

1l

a

m

r

o

Nl

a

m

r

o

Nl

a

m

r

o

Nl

a

m

r

o

Nz

H

M

6

6z

H

M

3

3z

H

M

8

4z

H

M

8

1

3

.

4

1

0l

a

m

r

o

Nl

a

m

r

o

N6

*

f

e

r

I

t

a

o

l

F

r

o

w

o

Lz

H

M

6

6w

o

Lz

H

M

8

4z

H

M

8

1

3

.

4

1

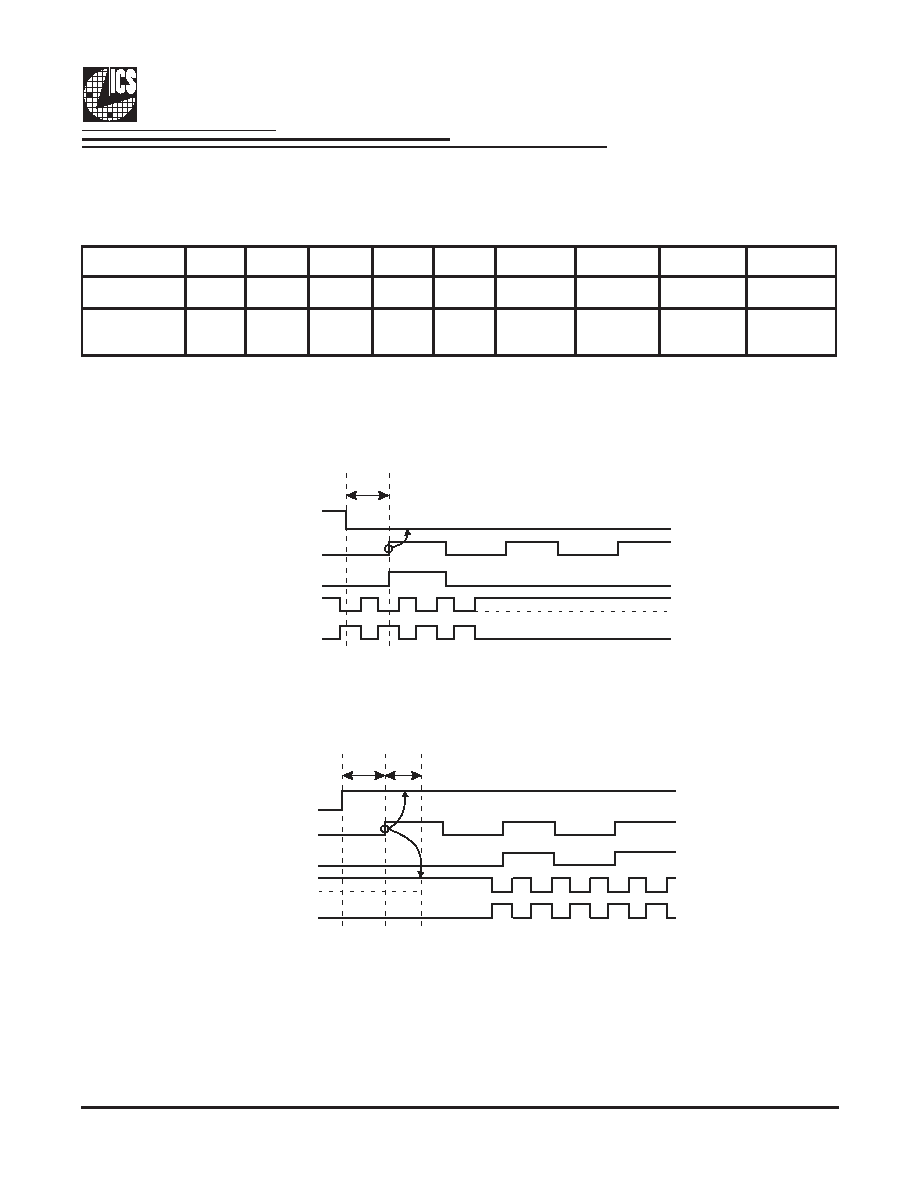

The clock samples the PCI_STOP# signal on a rising edge of PCIF clock. After detecting the PCI_STOP# assertion low, all

PCI[6:0] and stoppable PCIF[2:0] clocks will latch low on their next high to low transition. After the PCI clocks are latched low,

the SRC clock, (if set to stoppable) will latch high at Iref * 6 (or tristate if Byte 2 Bit 6 = 1) upon its next low to high transition and

the SRC# will latch low as shown below.

PCI_STOP#

Tsu

PCIF[2:0] 33MHz

PCI[6:0] 33MHz

SRC 100MHz

SRC# 100MHz

PCI_STOP# Assertion (transition from '1' to '0')

The de-assertion of the PCI_Stop# signal is to be sampled on the rising edge of the PCIF free running clock domain. After

detecting PCI_Stop# de-assertion, all PCI[6:0], stoppable PCIF[2:0] and stoppable SRC clocks will resume in a glitch free

manner.

PCI_STOP#

Tsu

Tdrive_SRC

PCIF[2:0] 33MHz

PCI[6:0] 33MHz

SRC 100MHz

SRC# 100MHz

PCI_STOP# - De-assertion

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 932S208DFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S208YGLNT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S401EGLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S401EFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S421BGLF | 333.33 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 932S208DGLF | 功能描述:時鐘合成器/抖動清除器 SERVER MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 932S208DGLFT | 功能描述:時鐘合成器/抖動清除器 SERVER MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 932S208YFLNT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Programmable Timing Control HubTM for Next Gen P4TM Processor |

| 932S208YGLNT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Programmable Timing Control HubTM for Next Gen P4TM Processor |

| 932S401EFLF | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。