- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24634 > 932S203YFT (INTEGRATED DEVICE TECHNOLOGY INC) 133.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號(hào): | 932S203YFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 133.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 0.300 INCH, GREEN, MO-118, SSOP-56 |

| 文件頁(yè)數(shù): | 13/18頁(yè) |

| 文件大小: | 243K |

| 代理商: | 932S203YFT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

IDTTM Frequency Generator with 133MHz Differential CPU Clocks

0601G—01/26/10

ICS932S203

Frequency Generator with 133MHz Differential CPU Clocks

4

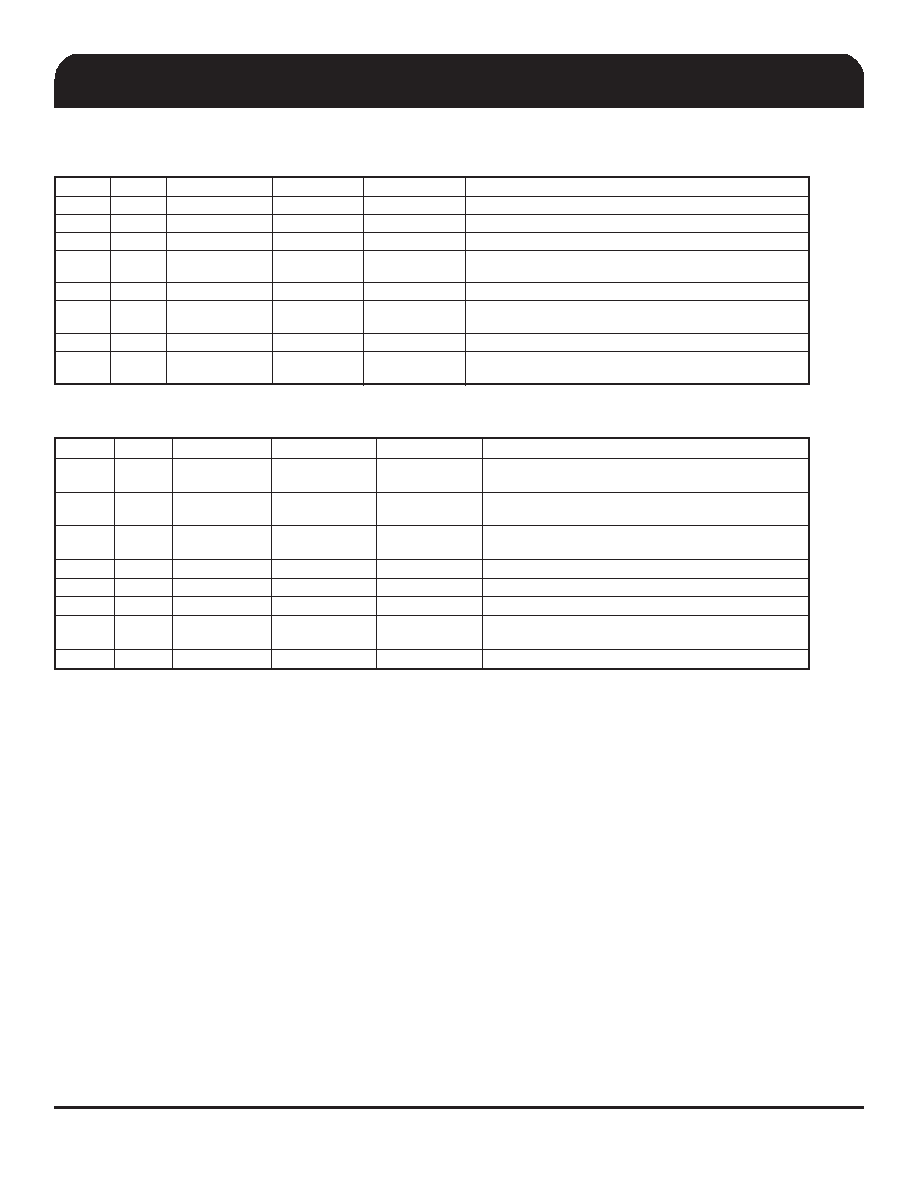

Byte 0: Control Register

Notes:

1. R= Read only RW= Read and Write

2. PWD = Power on Default

3. The purpose of this bit is to allow a system designer to implement PCI_STOP functionality in one of two ways. Wither the

system designer can choose to use the externally provided PCI_STOP# pin to assert and de-assert PCI_STOP

functionality via SMBus Byte 0 Bit 3.

In Hardware mode it is not allowed to write to the SMBus Byte 0 Bit3. In Software mode it is not allowed to pull the

external PCI_STOP pin low. This avoids the issues related with Hardware started and software stopped PCI_STOP

conditions. The clock chip is to be operated in the Hardware or Software PCI_STOP mode ONLY, it is not allowed to mix

these modes.

In Hardware mode the SMBus byte 0 Bit 3 is R/W and should reflect the status of the part. Whether or not the chip is in

PCI_STOP mode.

Functionality PCI_STOP mode should be entered when [(PCI_STOP#=0) or (SMBus Byte 0 Bit 3 = 0)].

Byte 1: Control Register

t

i

B#

n

i

Pe

m

a

ND

W

Pe

p

y

Tn

o

i

t

p

i

r

c

s

e

D

0

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

1

t

i

B5

50

S

FX

R

p

u

r

e

w

o

p

n

o

d

e

l

p

m

a

s

n

i

p

0

S

F

f

o

e

u

l

a

v

e

h

t

s

t

c

e

l

f

e

R

2

t

i

B0

41

S

FX

R

p

u

r

e

w

o

p

n

o

d

e

l

p

m

a

s

n

i

p

1

S

F

f

o

e

u

l

a

v

e

h

t

s

t

c

e

l

f

e

R

3

t

i

B4

3#

P

O

T

S

_

I

C

P

3

XR

#

P

O

T

S

_

I

C

P

f

o

e

u

l

a

v

e

h

t

s

t

c

e

l

f

e

R

:

e

d

o

m

e

r

a

w

d

r

a

H

D

W

P

n

o

d

e

l

p

m

a

s

n

i

p

4

t

i

B-

1

)

d

e

v

r

e

s

e

R

(

5

t

i

B5

3H

C

V

/

1

_

6

V

30

W

R

z

H

M

8

4

/

z

H

M

6

t

c

e

l

e

S

H

C

V

z

H

M

8

4

=

1

,

z

H

M

6

=

0

6

t

i

B-

0

)

d

e

v

r

e

s

e

R

(

7

t

i

B-

d

a

e

r

p

S

d

e

l

b

a

n

E

0W

Rn

O

d

a

e

r

p

S

=

1

,

f

O

d

a

e

r

p

S

=

0

t

i

B#

n

i

Pe

m

a

ND

W

Pe

p

y

Tn

o

i

t

p

i

r

c

s

e

D

0

t

i

B1

5

,

2

5

0

T

K

L

C

U

P

C

0

C

K

L

C

U

P

C

1W

Rd

e

l

b

a

n

E

=

1

d

e

l

b

a

s

i

D

=

0

1

t

i

B8

4

,

9

4

1

T

K

L

C

U

P

C

1

C

K

L

C

U

P

C

1W

Rd

e

l

b

a

n

E

=

1

d

e

l

b

a

s

i

D

=

0

2

t

i

B4

4

,

5

4

2

T

K

L

C

U

P

C

2

C

K

L

C

U

P

C

1W

Rd

e

l

b

a

n

E

=

1

d

e

l

b

a

s

i

D

=

0

3

t

i

B1

5

,

2

50

-

d

e

v

r

e

s

e

R

4

t

i

B8

4

,

9

40

-

d

e

v

r

e

s

e

R

5

t

i

B4

4

,

5

40

-

d

e

v

r

e

s

e

R

6

t

i

B4

5

,

3

5

3

T

K

L

C

U

P

C

3

C

K

L

C

U

P

C

1W

Rd

e

l

b

a

n

E

=

1

d

e

l

b

a

s

i

D

=

0

7

t

i

B3

40

L

E

S

T

L

U

MX

R

0

L

E

S

T

L

U

M

f

o

e

u

l

a

v

t

n

e

r

u

c

e

h

t

s

t

c

e

l

f

e

R

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 932S203YFLN | 133.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S208DG | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S208DGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S208DGT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 932S208DFLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 932S203YGLXT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Frequency Generator with 133MHz Differential CPU Clocks |

| 932S208DFLF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 SERVER MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 932S208DFLFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 SERVER MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 932S208DGLF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 SERVER MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 932S208DGLFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 SERVER MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。