- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376472 > 82C836A-20 (Electronic Theatre Controls, Inc.) Single-Chip 386sx AT PDF資料下載

參數(shù)資料

| 型號(hào): | 82C836A-20 |

| 廠(chǎng)商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Single-Chip 386sx AT |

| 中文描述: | 單芯片386sx在 |

| 文件頁(yè)數(shù): | 151/205頁(yè) |

| 文件大?。?/td> | 3878K |

| 代理商: | 82C836A-20 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)當(dāng)前第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)

mid-T1. Since the earliest that the 82C836 could assert -READY again is during the

third T2 after T1 (early wait state enabled), the first T2 after T1 is available for external

logic to assert -READY without conflicting with the 82C836.

The 82C836 samples -LBA and -READY at the end of the first T2 after T1. -READY

active at that time terminates the cycle. -LBA active at that time causes the 82C836 to

look for -READY at the end of each subsequent T2 state. The cycle terminates when the

external logic asserts -READY. -LBA is ignored and is ‘‘don’t care’’ at all times other

than at the end of the first T2 after T1.

If the external logic asserts both -LBA and -READY at the end of the first T2 (not a valid

combination), the cycle terminates just as if -READY alone had been asserted.

The net performance effect of local cache is as follows:

Greatly increased percentage of two T-state memory reads due to high cache hit ratio

(without cache, two T-state memory reads would still be possible in pipelined page

mode, but the hit ratio would be considerably lower than with a cache).

Cache read misses increase from two T-state minimum to four T-states for -CAS only

memory reads. Since cache read misses occur far less often with cache than without

it, this penalty for cache read misses should have only a minor impact on overall

system performance.

Page hit writes can occur in zero wait states, as compared to one wait state minimum

in noncache modes.

Coprocessor Timing

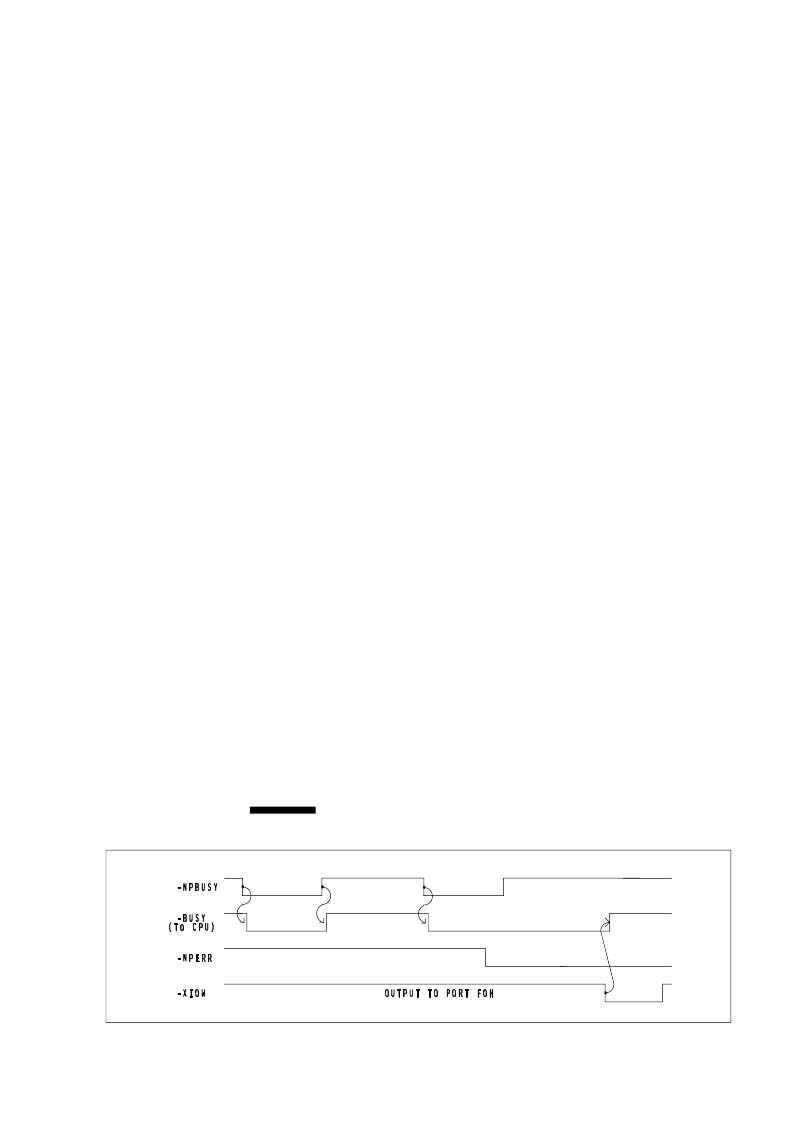

Figure 11-11 shows the relationship between the coprocessor busy and error signals

and the busy signal sent to the CPU. Normally, -BUSY to the CPU simply follows

-NPBUSY from the coprocessor. When a coprocessor exception occurs (-NPERR

asserted), -BUSY to the CPU is latched (active) until the CPU acknowledges it by

performing an I/O write to prot F0H. This protocol is AT-compatible and differs from

the ‘‘generic’’ coprocessor interface internal to the 80386sx CPU. In particular, the

-ERROR input to the CPU should be tied high, and AT-compatible software will rely

on interrupt level 13 for reporting coprocessor exceptions. The -NPERR signal from

the coprocessor is eventually cleared by I/O writes to the coprocessor sometime after

the output to port F0H.

Figure 11-11.

Coprocessor Timing

System Timing Relationships

CPU Access to AT-Bus

I

Chips and Technologies, Inc.

P R E L I M I N A R Y

Revision 3.0

11-19

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 82C836B | Single-Chip 386sx AT |

| 82C862 | FireLink USB Dual Controller Quad Port USB |

| 82C931 | Plug and Play Integrated Audio Controller |

| 82S09 | 576-BIT BIPOLAR RAM (64 X 9) |

| 82S19 | 576-BIT BIPOLAR RAM (64 X 9) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 82C836B | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Single-Chip 386sx AT |

| 82C83H | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:CMOS Octal Latching Inverting Bus Driver |

| 82C84 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:CMOS Clock Generator Driver |

| 82C84A | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:CMOS Clock Generator Driver |

| 82C84A/B | 制造商: 功能描述: 制造商:undefined 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。