- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16168 > 78P2351-DB/ECLM (Maxim Integrated Products)BOARD DEMO 78P2351 W/OPT MODULE PDF資料下載

參數(shù)資料

| 型號: | 78P2351-DB/ECLM |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 40/42頁 |

| 文件大小: | 0K |

| 描述: | BOARD DEMO 78P2351 W/OPT MODULE |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁

78P2351

Single Channel

OC-3/ STM1-E/ E4 LIU

Page: 7 of 42

2006 Teridian Semiconductor Corporation

Rev. 2.4

Transmit Driver

In CMI (electrical) mode, the CMIP/N pins are biased

and terminated off-chip.

They interface to 75

coaxial cable through a 1:1 wideband transformer

and coaxial RF connectors. Reference application

notes for schematic and layout guidelines.

The transmitter encodes the data using CMI line

coding and shapes an analog signal to meet the

appropriate ITU-T G.703 template. The CMI outputs

are tri-stated during transmit disable and transmit

power-down for redundancy applications.

Note: To avoid reflections causing unwanted

board noise, it’s recommended to power-down

unused transmit ports that are not terminated

with cable to an Rx input port.

When the CMI pin is low, the chip is in Fiber (NRZ

pass-through) mode and interfaces directly to an

optical transceiver module. The ECLP/N pins are

internally biased and output NRZ data at LVPECL

levels. The CMI driver, encoder and decoder are

disabled in Fiber (NRZ) mode.

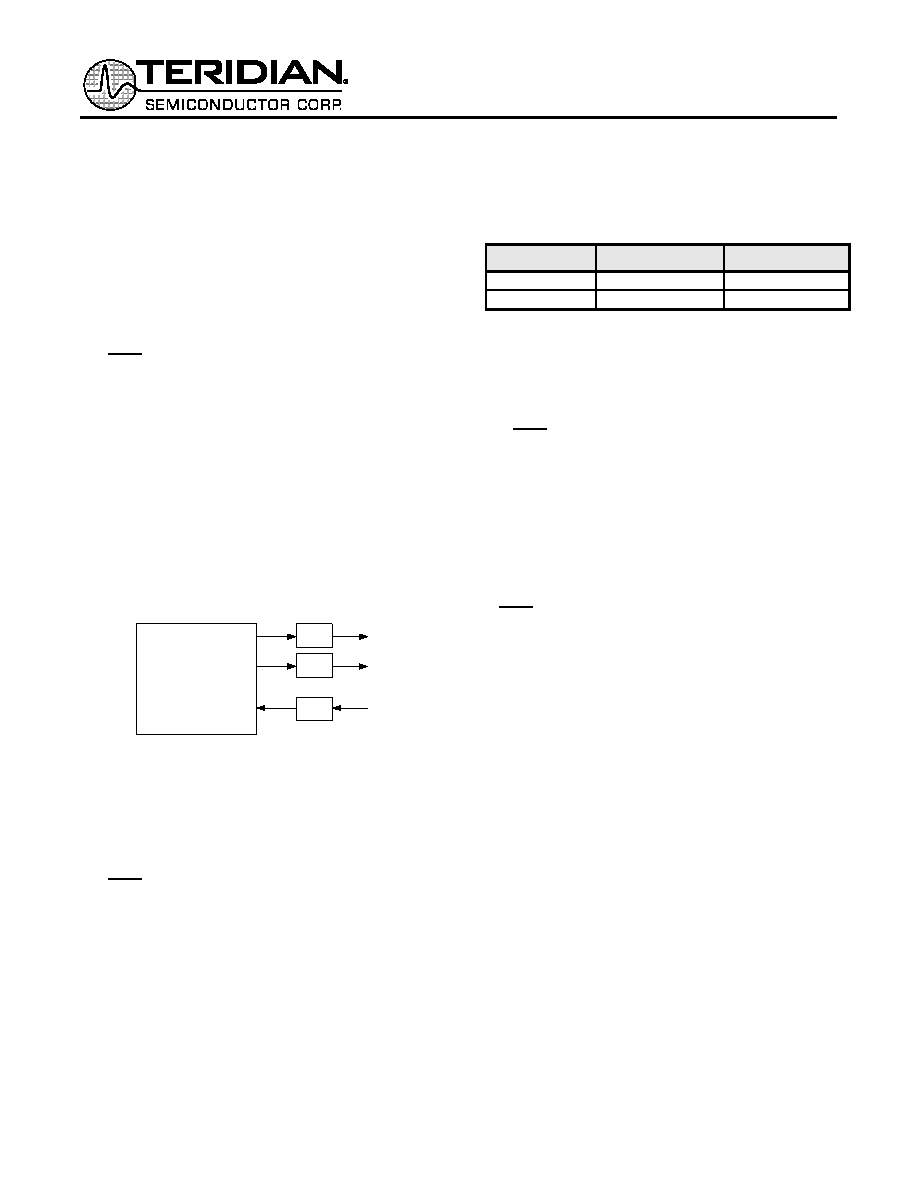

Transmit Monitor Mode

An optional redundant transmit output is available in

CMI mode for transmit monitoring. These outputs

(CMI2P/N) are enabled when the RCSL pin or RCSL

register bit is activated.

TDK

78P2351

RXP/N

CMIP/N

XFMR

CMI

Coax

CMI2P/N

XFMR

CMI

Coax

Figure 6: Transmit Monitor Output

Clock Synthesizer

The transmit clock synthesizer is a low-jitter DLL that

generates a 278.528/311.04 MHz clock for the CMI

encoder. It is also used in both the receive and

transmit sides for clock and data recovery.

Note: This 2x line rate clock is also available at

the

TXCKxP/N

pins

for

downstream

synchronization or system debug.

Transmit Backplane Equalizer

An optional fixed LVPECL equalizer is integrated in

the transmit path for architectures that use LIUs on

active interface cards.

The fixed equalizer can

compensate for up to 1.5m of trace and can be

enabled by the TXOUT1 pin or TXEQ bit as follows:

TXOUT1 pin

TXEQ bit

Tx Equalizer

Low

1

Enabled

Float

0

Disabled

Transmit Loss of Lock

In transmit modes using the integrated CDR, the

78P2351 will declare a loss of lock condition when

there is no valid signal detected at the SIDP/N data

inputs.

Note: The Tx LOL indicator is invalid and

undefined when the parallel (nibble) interface is

selected.

POWER-DOWN FUNCTION

Power-down control is provided to allow the

78P2351 to be shut off.

Transmit and receive

power-down can be set independently through SW

control.

Global power-down is achieved by

powering down both the transmitter and receiver.

Note: The serial interface and configuration

registers are not affected by power-down.

In HW mode, the transmitters can be powered down

using the TXPD control pin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M1RXK-2640K | IDC CABLE - MPR26K/MC26F/X |

| GSM08DRTN-S13 | CONN EDGECARD 16POS .156 EXTEND |

| M3WWK-2606J | IDC CABLE - MPL26K/MC26G/MPL26K |

| GMM08DRTN-S13 | CONN EDGECARD 16POS .156 EXTEND |

| 383LX821M450B052VS | CAP ALUM 820UF 450V 20% SNAP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 78P2351-IGT | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Single Channel OC-3/ STM1-E/ E4 LIU |

| 78P2351-IGT/F | 功能描述:接口 - 專用 Single Ch OC-3/STM-1e/E4 LIU RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| 78P2351-IGTR | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Single Channel OC-3/ STM1-E/ E4 LIU |

| 78P2351-IGTR/F | 功能描述:接口 - 專用 Single Ch OC-3/STM-1e/E4 LIU RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| 78P2351R | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Serial 155M NRZ to CMI Converter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。