- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382823 > 74LVTH543 (Fairchild Semiconductor Corporation) Low Voltage Octal Registered Transceiver with 3-STATE Outputs PDF資料下載

參數(shù)資料

| 型號(hào): | 74LVTH543 |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | Low Voltage Octal Registered Transceiver with 3-STATE Outputs |

| 中文描述: | 低壓八路注冊(cè)收發(fā)器三態(tài)輸出 |

| 文件頁(yè)數(shù): | 1/7頁(yè) |

| 文件大小: | 66K |

| 代理商: | 74LVTH543 |

2000 Fairchild Semiconductor Corporation

DS012448

www.fairchildsemi.com

April 2000

Revised April 2000

7

74LVTH543

Low Voltage Octal Registered Transceiver

with 3-STATE Outputs

General Description

The LVTH543 octal transceiver contains two sets of D-type

latches for temporary storage of data flowing in either

direction. Separate Latch Enable and Output Enable inputs

are provided for each register to permit independent con-

trol of inputting and outputting in either direction of data

flow.

The LVTH543 data inputs include bushold, eliminating the

need for external pull-up resistors to hold unused inputs.

This octal registered transceiver is designed for low-volt-

age (3.3V) V

CC

applications, but with the capability to pro-

vide a TTL interface to a 5V environment. The LVTH543 is

fabricated with an advanced BiCMOS technology to

achieve high speed operation similar to 5V ABT while

maintaining a low power dissipation.

Features

I

Input and output interface capability to systems at

5V V

CC

I

Bushold data inputs eliminate the need for external pull-

up resistors to hold unused inputs

I

Live insertion/extraction permitted

I

Power Up/Down high impedance provides glitch-free

bus loading

I

Outputs source/sink

32 mA/

+

64 mA

I

Functionally compatible with the 74 series 543

I

Latch-up performance exceeds 500 mA

Ordering Code:

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

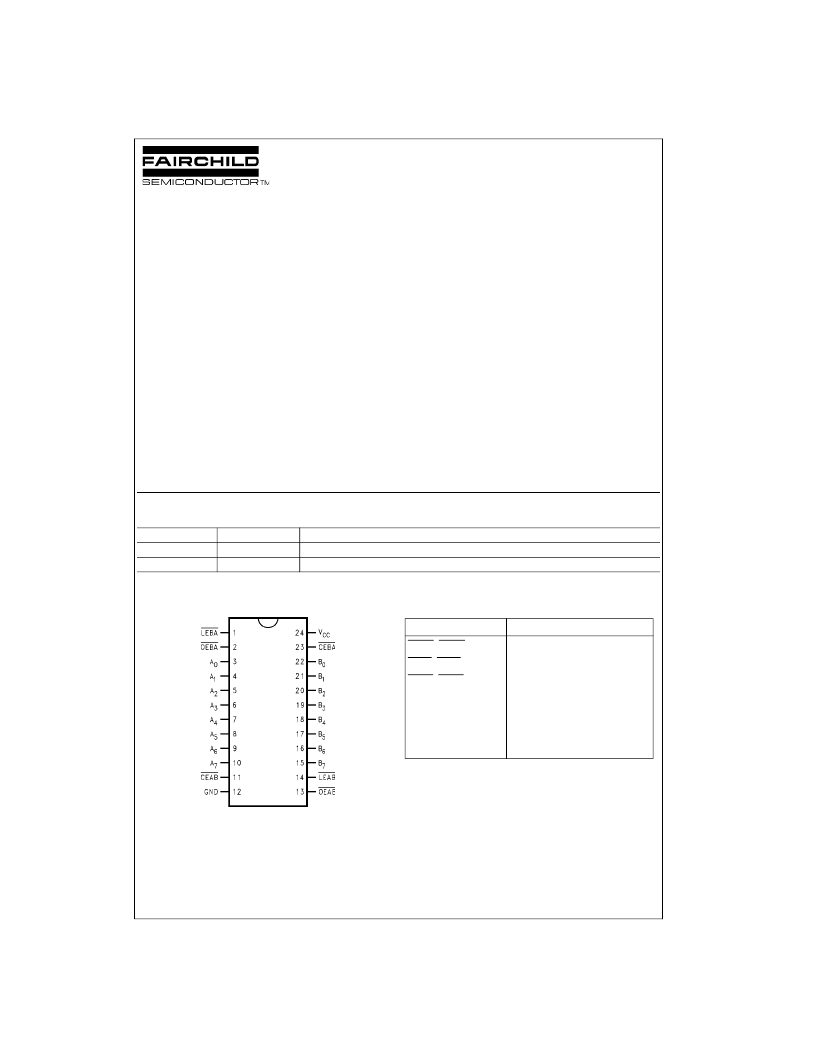

Connection Diagram

Pin Descriptions

Order Number

74LVTH543WM

74LVTH543MTC

Package Number

M24B

MTC24

Package Description

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide

24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Pin Names

Description

OEAB, OEBA

Output Enable Inputs

LEAB, LEBA

Latch Enable Inputs

CEAB, CEBA

Chip Enable Inputs

A

0

–A

7

Side A Inputs or

3-STATE Outputs

B

0

–B

7

Side B Inputs or

3-STATE Outputs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LVTH543MTC | Quadruple Positive-NOR Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 85 |

| 74LVTH573MTCX_NL | Low Voltage Octal Transparent Latch with 3-STATE Outputs |

| 74LVTH573 | Quadruple Positive-NOR Gates With Schmitt-Trigger Inputs 14-TSSOP -40 to 85 |

| 74LVTH573MSA | Low Voltage Octal Transparent Latch with 3-STATE Outputs |

| 74LVTH573MSAX | Quadruple Positive-OR Gates With Schmitt-Trigger Inputs 14-SOIC -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LVTH543_ZBB3026B WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| 74LVTH543MTC | 功能描述:總線收發(fā)器 Octal Reg Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74LVTH543MTCX | 功能描述:總線收發(fā)器 Octal Reg Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74LVTH543WM | 功能描述:總線收發(fā)器 Octal Reg Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74LVTH543WMX | 功能描述:總線收發(fā)器 Octal Reg Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。