- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360436 > 74F524SCX (FAIRCHILD SEMICONDUCTOR CORP) Magnitude Comparator PDF資料下載

參數(shù)資料

| 型號: | 74F524SCX |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Magnitude Comparator |

| 中文描述: | F/FAST SERIES, 8-BIT MAGNITUDE COMPARATOR, TRUE OUTPUT, PDSO20 |

| 封裝: | 0.300 INCH, MS-013, SOIC-20 |

| 文件頁數(shù): | 3/14頁 |

| 文件大?。?/td> | 131K |

| 代理商: | 74F524SCX |

Philips Semiconductors

Product specification

74F524

8-bit register comparator (open collector + 3-State)

1990 Aug 07

3

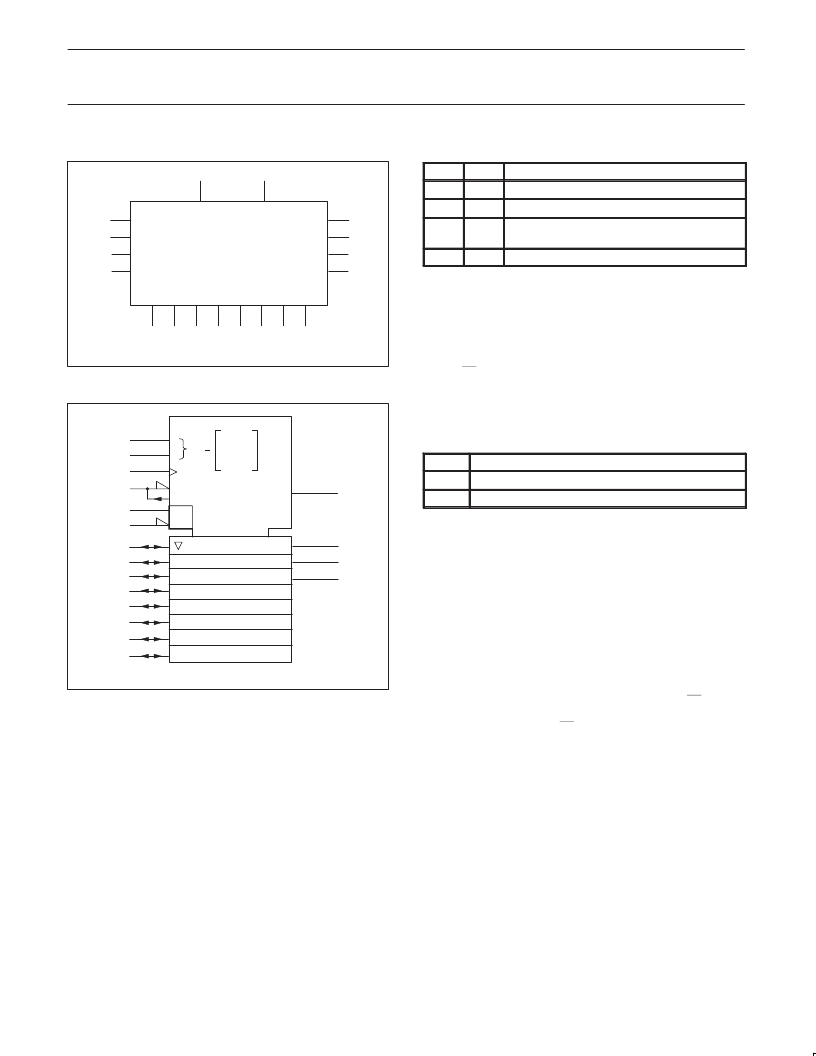

LOGIC SYMBOL for 74F456

M

SE

I/O0

I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7

S1

CP

S0

12

18

19

11

1

2

3

4

5

6

7

8

9

SF00971

V

GND = Pin 10

= Pin 20

C/SI

17

GT

EQ

LT

14

15

13

C/SO

16

LOGIC SYMBOL (IEEE/IEC) for 74F456

SF00972

&

G7

1

2

3

5

6

7

8

9

11

18

17

13

COMP

19

12

0

3

M

0

1

4

3, 4D

14

15

16

2D

1,5,6,7>I/O

1,5,6,7<I/O

1,5,6,7=I/O

M6 TWO’s COMPLEMENT

M5 MAGNITUDE

C4/2/4

0=HOLD

1=READ

2=SHIFT

3=LOAD

FUNCTIONAL DESCRIPTION

The 74F524 contains eight D-type flip-flops connected as a shift

register with provision for either parallel or serial loading. Parallel

data may be read from or loaded into the registers via the data bus

I/O0–I/O7. Serial data is loaded into the register from the C/SI input

and may be shifted through the register and out through the C/SO

output. Both parallel and serial data entry occurs on the rising edge

of the clock (CP). The operation of the shift register is controlled by

two signals, S0 and S1, according to the Select Function Table. The

3-State parallel output buffers are enabled only in the READ mode.

SELECT FUNCTION TABLE

S0

S1

OPERATION

L

L

HOLD–Retains data in shift register

L

H

READ–Read contents in register onto data bus

H

L

SHIFT–Allows serial shifting on next rising clock

edge

H

H

LOAD–Load data on bus into register

H = High voltage level

L

= Low voltage level

One port of an 8-bit comparator is attached to the data bus while the

other port is tied to the outputs of the internal register. Three

active-OFF Open Collector outputs indicate whether the contents

held in the shift register are ‘greater than’ (GT). ‘less than’ (LT), or

‘equal to’ (EQ) the data on the input bus. A High signal on the Status

Enable (SE) input disables these outputs to the OFF state. A mode

control (M) input allows selection between a straightforward

magnitude compare or a comparison between Two’s complement

numbers.

NUMBER REPRESENTATION SELECT TABLE

M

OPERATION

L

Magnitude compare

H

Two’s Complement compare

H = High voltage level

L

= Low voltage level

For ‘greater than’ or ‘less than’ detection, the C/SI input must be

held High, as indicated in the Function Table. The internal logic is

arranged such that a Low signal on the C/SI input places the

‘greater than’ and ‘less than’ outputs in their off state. (Note that this

off state serves also as the active state when C/SI is High. It is

intended for use in expansion to word lengths greater than 8 bits

using multiple 74S524s as explained in the next 3 paragraphs.) The

C/SO output will be forced High if the ‘equal to’ status condition

exists; otherwise, C/SO will be held Low.

Word length expansion (in groups of 8 bits) can be achieved by

connecting the C/SO output of the more significant byte to the C/SI

input of the next less significant byte and also to its own SE input

(see Application Figure 1). The CS/I input of the most significant

device is held High while the SE input of the least significant device

is held Low. The corresponding status outputs are AND-wired

together. In the case of two’s complement number compare, only the

Mode input to the most significant device should be High. the Mode

inputs to all other cascaded devices are held Low.

Suppose that an inequality condition is detected in the most

significant device. Assuming that the byte stored in the register is

greater than the byte on the data bus, then the EQ and LT outputs

will be pulled Low, whereas the GT output will float High. Also, the

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74F5300 | Fiber optic LED driver(光纖LED驅(qū)動器) |

| 74F5302 | Fiber Optic Dual LED/clock Driver(光纖雙路LED/時鐘驅(qū)動器) |

| 74F533DC | 8-Bit D-Type Latch |

| 74F533SCX | 8-Bit D-Type Latch |

| 74F533SJX | 8-Bit D-Type Latch |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74F525 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Programmable Counter |

| 74F525 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| 74F525DC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Timer Circuit |

| 74F525PC | 制造商:Texas Instruments 功能描述: 制造商:National Semiconductor Corporation 功能描述:F/FAST SERIES, ASYN POSITIVE EDGE TRIGGERED DOWN DIVIDE BY N COUNTER, PDIP28 |

| 74F525PCX | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Programmable Counter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。