- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368731 > 16F628 (Microchip Technology Inc.) CAT 5E CROSSOVER PATCH CORD CABLE BLUE 1 FT PDF資料下載

參數(shù)資料

| 型號: | 16F628 |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | CAT 5E CROSSOVER PATCH CORD CABLE BLUE 1 FT |

| 中文描述: | 基于閃存的8位CMOS微控制器 |

| 文件頁數(shù): | 122/168頁 |

| 文件大小: | 3760K |

| 代理商: | 16F628 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁當(dāng)前第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁

PIC16F627A/628A/648A

DS40044A-page 120

Preliminary

2002 Microchip Technology Inc.

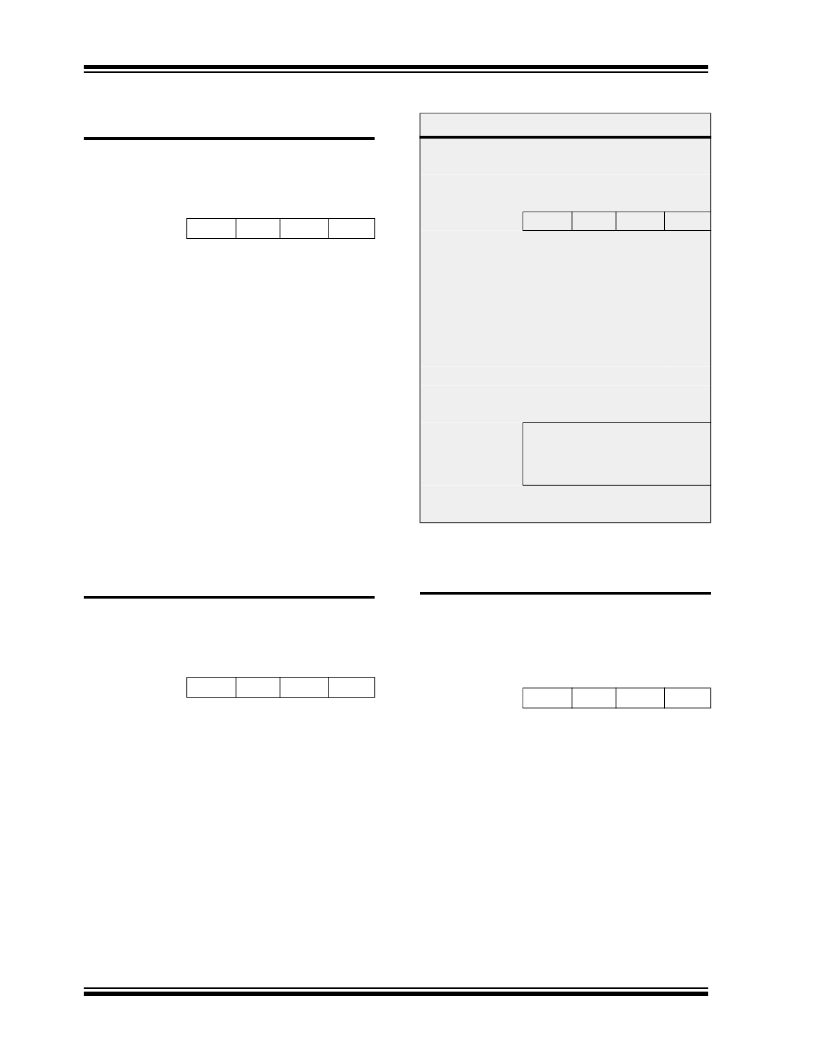

MOVWF

Move W to f

Syntax:

[

label

] MOVWF f

Operands:

0

≤

f

≤

127

Operation:

(W)

→

(f)

Status Affected:

None

Encoding:

00

0000

1fff

ffff

Description:

Move data from W register to regis-

ter 'f'

.

Words:

1

Cycles:

1

Example

MOVWF

REG1

Before Instruction

REG1 = 0xFF

W

After Instruction

REG1 = 0x4F

W

= 0x4F

= 0x4F

NOP

No Operation

Syntax:

[

label

] NOP

Operands:

None

Operation:

No operation

Status Affected:

None

Encoding:

00

0000

0xx0

0000

Description:

No operation.

Words:

1

Cycles:

1

Example

NOP

OPTION

Load Option Register

Syntax:

[

label

] OPTION

Operands:

None

(W)

→

OPTION

Operation:

Status Affected:

None

Encoding:

00

0000

0110

0010

Description:

The contents of the W register are

loaded in the OPTION register.

This instruction is supported for

code compatibility with PIC16C5X

products. Since OPTION is a

readable/writable register, the

user can directly address it. Using

only register instruction such as

MOVWF.

Words:

1

Cycles:

1

Example

To maintain upward compatibil-

ity with future PICmicro

prod-

ucts, do not use this

instruction.

RETFIE

Return from Interrupt

Syntax:

[

label

] RETFIE

Operands:

None

Operation:

TOS

→

PC,

1

→

GIE

Status Affected:

None

Encoding:

00

0000

0000

1001

Description:

Return from Interrupt. Stack is

POPed and Top of Stack (TOS)

is loaded in the PC. Interrupts

are enabled by setting Global

Interrupt Enable bit, GIE

(INTCON<7>). This is a two-

cycle instruction.

Words:

1

Cycles:

2

Example

RETFIE

After Interrupt

PC = TOS

GIE = 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 16M0 | PC SERIAL MODEM CBL 50 FT |

| 16M0B | APPLE IIC CABLE TO IWRTR MODEM |

| 16M0BC | KEYBD.EXT. MINI DIN 4 MM 6 FT |

| 16M0BS | KEYBD.EXT. MINI DIN 4 MM 10 FT |

| 16M0D | MINI DIN 8, MALE-MALE 10 FT. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 16F630 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:14-Pin FLASH-Based 8-Bit CMOS Microcontrollers |

| 16F684-I | 制造商:Microchip Technology Inc 功能描述: |

| 16F6H | 制造商:EDAL 制造商全稱:EDAL 功能描述:Silicon High Voltage Assembly |

| 16F6H1 | 制造商:EDAL 制造商全稱:EDAL 功能描述:Silicon High Voltage Assembly |

| 16F7674 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SMD TWEEZER HEAD |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。