- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄2121 > XRT91L32IQTR (Exar Corporation)IC TXRX SONET/SDH 8BIT 100QFP PDF資料下載

參數(shù)資料

| 型號(hào): | XRT91L32IQTR |

| 廠(chǎng)商: | Exar Corporation |

| 文件頁(yè)數(shù): | 10/37頁(yè) |

| 文件大小: | 0K |

| 描述: | IC TXRX SONET/SDH 8BIT 100QFP |

| 產(chǎn)品變化通告: | XRT91L32IQ(TR) Obsolescence 12/Oct/2010 |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 類(lèi)型: | 收發(fā)器 |

| 規(guī)程: | SONET/SDH |

| 電源電壓: | 3.3V |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 100-BQFP |

| 供應(yīng)商設(shè)備封裝: | 100-QFP(14x20) |

| 包裝: | 帶卷 (TR) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

XRT91L32

xr

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

REV. 1.0.2

16

2.4

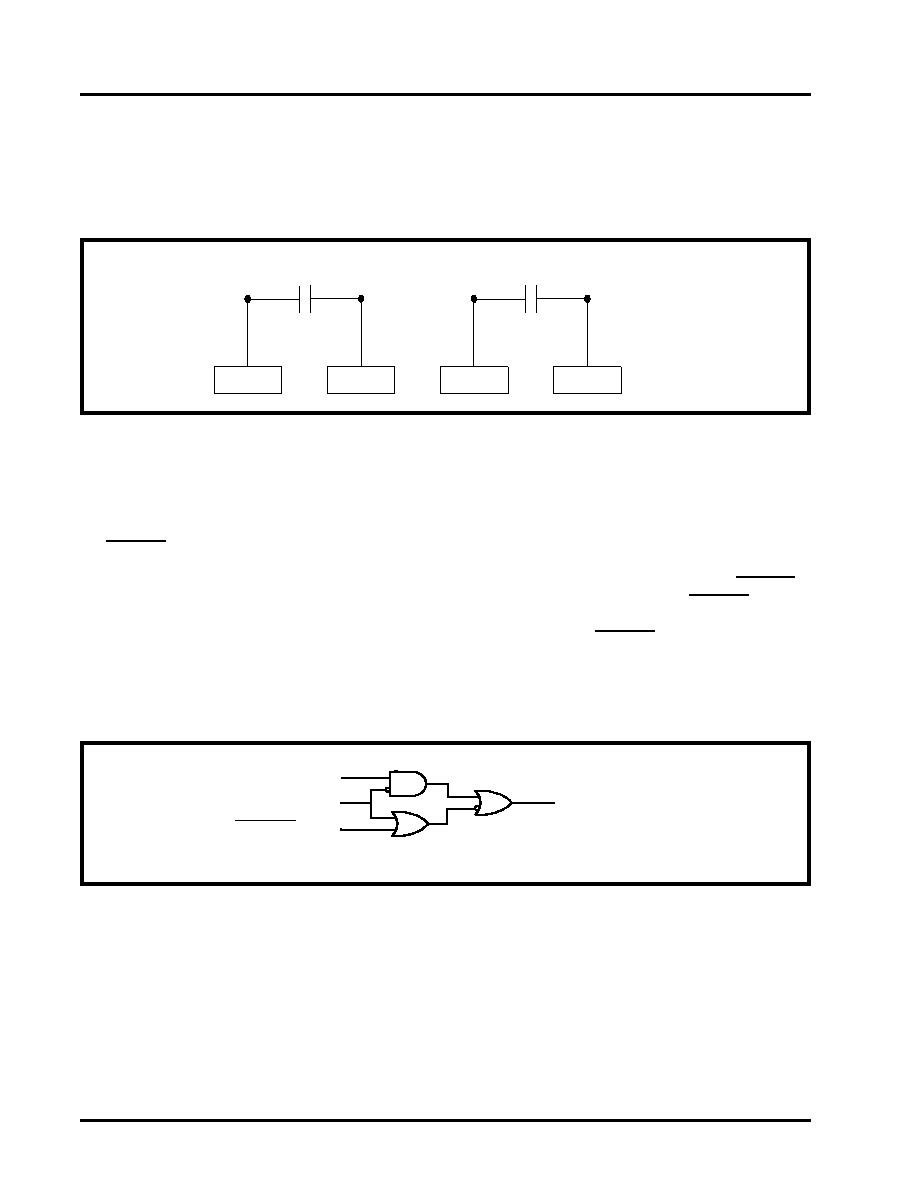

External Receive Loop Filter Capacitors

These external loop filter 0.47

μF non-polarized capacitors provide the necessary components to achieve the

required receiver jitter performance. They must be well isolated to prohibit noise entering the CDR block and

should be placed as close to the pins as much as possible. Figure 6 shows the pin connections and external

loop filter components. These two non-polarized capacitors should be of +/- 10% tolerance.

2.5

Loss Of Signal

XRT91L32 supports internal Loss of Signal detection (LOS) and external LOS detection. The internal Loss of

Signal Detector monitors the incoming data stream and if the incoming data stream has no transition

continuously for more than 128 bit periods, Loss of Signal is declared. This LOS detection will be removed

when the circuit detects 16 transitions in a 128 bit period sliding window. Pulling the corresponding DLOSDIS

signal to a high level will disable the internal LOS detection circuit. The external LOS function is supported by

the LOSEXT input. The Single-Ended LVPECL input usually comes from the optical module through an output

usually called “SD” or “FLAG” which indicates the lack or presence of optical power. Depending on the

manufacturer of these devices the polarity of this signal can be either active "Low" or active "High." LOSEXT is

an active "Low" signal requiring a low level to assert or invoke a forced LOS. The external LOSEXT input pin

and internal LOS detector are gated to control detection and declaration of Loss of Signal (see Figure 7.)

Whenever LOS is internally detected or an external LOS is asserted thru the LOSEXT pin, the XRT91L32 will

automatically force the receive parallel data output to a logic state "0" for the entire duration that a LOS

condition is declared. This acts as a receive data mute upon LOS function to prevent random noise from being

misinterpreted as valid incoming data.

FIGURE 6. EXTERNAL LOOP FILTERS

FIGURE 7. LOS DECLARATION CIRCUIT

CAP2N

CAP1N

0.47uF

non-polarized

CAP2P

CAP1P

0.47uF

non-polarized

Pin 66

Pin 63

Pin 64

Pin 65

Intern al L O S D etect

DLO S D IS

LO SEXT ( SD )

LO S D e cla ration

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT91L80IB-F | IC TXRX SONET/SDH 4BIT 196STBGA |

| ZSD100N8TA | IC DRIVER SIREN 8-SOIC |

| ZXCD1210JB16TA | IC AMP AUDIO CLASS D 16QFN |

| ZXFV203N14TC | IC AMP VIDEO CFA 3CHAN 14SOIC |

| 020189 | FAN 115VAC 254X89MM CLE2T2 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L32IQTR-F | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L33 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |

| XRT91L33AIG-F | 制造商:Exar Corporation 功能描述:CDR 155.52Mbps/622.08Mbps SONET/SDH 20-Pin TSSOP |

| XRT91L33ES | 功能描述:界面開(kāi)發(fā)工具 Eval System for XRT91L33 Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類(lèi)型:RS-485 工具用于評(píng)估:ADM3485E 接口類(lèi)型:RS-485 工作電源電壓:3.3 V |

| XRT91L33IG | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。