- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16552 > XR16M770IL32-0C-EB (Exar Corporation)EVAL BOARD FOR XR16M770-C 32QFN PDF資料下載

參數(shù)資料

| 型號(hào): | XR16M770IL32-0C-EB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 32/52頁 |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR16M770-C 32QFN |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

XR16M770

38

1.62V TO 3.63V HIGH PERFORMANCE UART WITH 64-BYTE FIFO

REV. 1.0.2

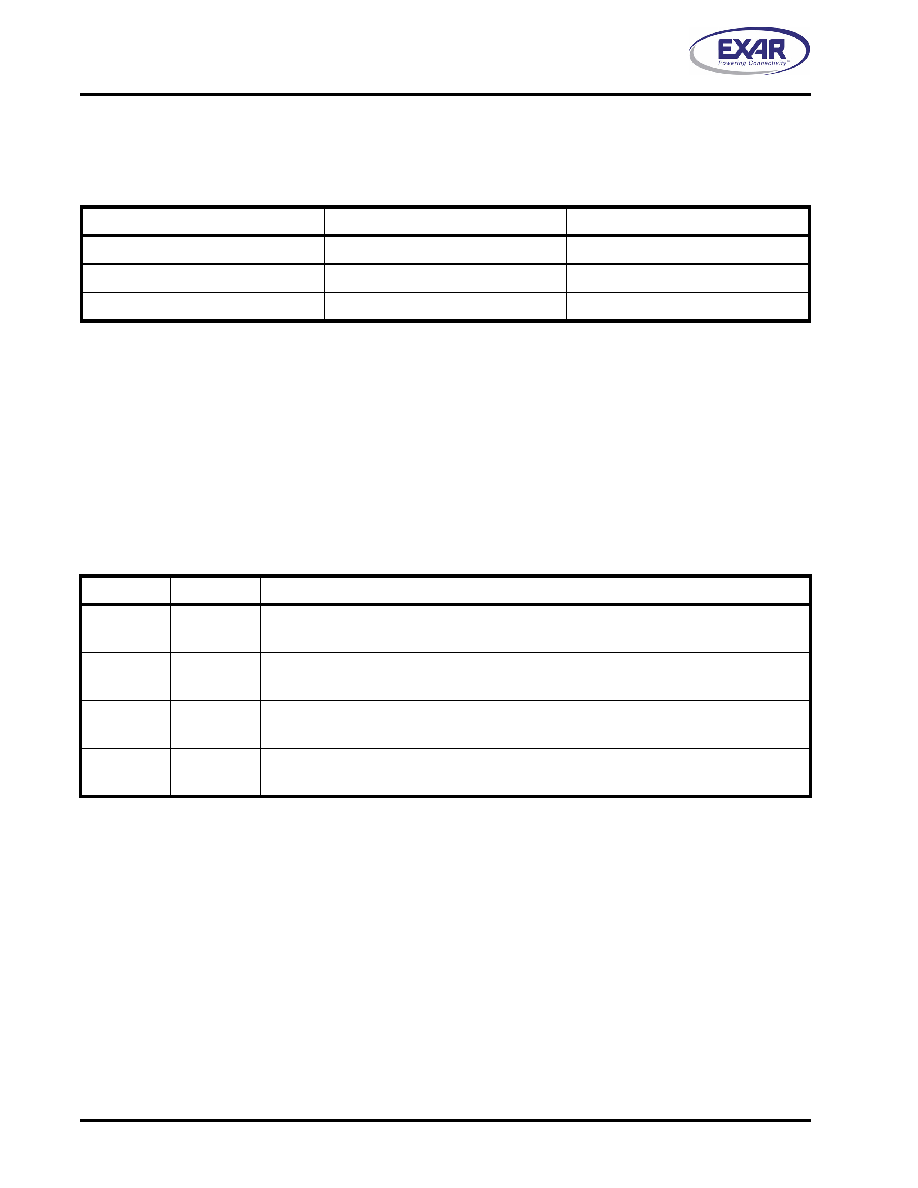

DLD[5:4]: Sampling Rate Select

These bits select the data sampling rate. By default, the data sampling rate is 16X. The maximum data rate will

double if the 8X mode is selected and will quadruple if the 4X mode is selected. See Table 14 below.

TABLE 14: SAMPLING RATE SELECT

SAMPLING RATE

0

16X

0

1

8X

1

X

4X

DLD[6]: Independent BRG enable

Logic 0 = The Transmitter and Receiver uses the same Baud Rate Generator. (default).

Logic 1 = The Transmitter and Receiver uses different Baud Rate Generators. Use DLD[7] for selecting

which baud rate generator to configure.

DLD[7]: BRG select

When DLD[6] = 1, this bit selects whether the values written to DLL, DLM and DLD[5:0] will be for the Transmit

Baud Rate Generator or the Receive Baud Rate Generator. When DLD[6] = 0 (same Baud Rate Generator

used for both TX and RX), this bit must be a logic 0 to properly write to the appropriate DLL, DLM and

DLD[5:0]. .

TABLE 15: BRG SELECT

0

Transmitter and Receiver uses same BRG.

Writing to DLL, DLM and DLD[5:0] configures the BRG for both the TX and RX.

0

1

Transmitter and Receiver uses different BRGs.

Writing to DLL, DLM and DLD[5:0] configures the BRG for TX.

1

Transmitter and Receiver uses different BRGs.

Writing to DLL, DLM and DLD[5:0] configures the BRG for RX.

1

0

Transmitter and Receiver uses same BRG.

Writing to DLL, DLM and DLD[5:0] has no effect on BRG used by the TX and RX.

4.14

Trigger Level Register (TRG) - Write-Only

User Programmable Transmit/Receive Trigger Level Register.

TRG[7:0]: Trigger Level Register

These bits are used to program desired trigger levels when trigger Table-D is selected. FCTR bit-7 selects

between programming the RX Trigger Level (a logic 0) and the TX Trigger Level (a logic 1).

4.15

RX/TX FIFO Level Count Register (FC) - Read-Only

This register replaces SPR (during a read) and is accessible when FCTR[6] = 1. This register is also

accessible when LCR = 0xBF. It is suggested to read the FIFO Level Count Register at the Scratchpad

Register location when FCTR bit-6 = 1. See Table 12.

DLD[5]

DLD[4]

DLD[7]

DLD[6]

BRG

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX16922ATPK/V+ | IC DCDC CONV STPDN DL LDO 20TQFN |

| MAX16922ATPJ/V+ | IC DCDC CONV STPDN DL LDO 20TQFN |

| H3BBH-3418M | IDC CABLE - HSR34H/AE34M/HSR34H |

| MAX16922ATPI/V+T | IC PMIC MED PWR AUTO 28V 20TQFN |

| H3BKH-4018G | IDC CABLE - HSR40H/AE40G/HPK40H |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16M770IL32-F | 功能描述:UART 接口集成電路 1.8 HIGH PERFORMANCE UART W/64 RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16M770IL32TR-F | 制造商:Exar Corporation 功能描述:UART 1-CH 64Byte FIFO 1.8V/2.5V/3.3V 32-Pin QFN EP T/R 制造商:Exar Corporation 功能描述:XR16M770IL32TR-F |

| XR16M780 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE UART WITH 64-BYTE FIFO |

| XR16M780IB25 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE UART WITH 64-BYTE FIFO |

| XR16M780IB25-0C-EB | 功能描述:界面開發(fā)工具 Eval Board for XR16M780IB25 Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。