- 您現在的位置:買賣IC網 > PDF目錄385956 > XR1002 (MIMIX BROADBAND INC) 18.0-34.0 GHz GaAs MMIC Receiver PDF資料下載

參數資料

| 型號: | XR1002 |

| 廠商: | MIMIX BROADBAND INC |

| 元件分類: | 衰減器 |

| 英文描述: | 18.0-34.0 GHz GaAs MMIC Receiver |

| 中文描述: | RF/MICROWAVE DOWN CONVERTER |

| 封裝: | PLASTIC, DIE-10 |

| 文件頁數: | 6/10頁 |

| 文件大?。?/td> | 413K |

| 代理商: | XR1002 |

Page 6 of 10

App Note [1] Biasing

- As shown in the bonding diagram, this device is operated with both stages in parallel, and can

be biased for low noise performance or high power performance. Low noise bias is nominally Vd=4.5V, Id=135mA and is

the recommended bias condition. More controlled performance will be obtained by separately biasing Vd1 and Vd2

each at 4.5V, 65mA. Power bias may be as high as Vd=5.5V, Id=270mA with all stages in parallel, or most controlled

performance will be obtained by separately biasing Vd1 and Vd2 each at 5.5V, 135mA. Attenuator bias, Vg3, can be

adjusted from 0.0 to -1.2V with 0.0V providing maximum attenuation and -1.2V providing minimum attenuation. Image

reject mixer bias, Vg4, should nominally be -0.8V to minimize sensitivity of mixer performance to LO level. It is also

recommended to use active biasing to keep the currents constant as the RF power and temperature vary; this gives the

most reproducible results. Depending on the supply voltage available and the power dissipation constraints, the bias

circuit may be a single transistor or a low power operational amplifier, with a low value resistor in series with the drain

supply used to sense the current. The gate of the pHEMT is controlled to maintain correct drain current and thus drain

voltage. The typical gate voltage needed to do this is -0.5V. Typically the gate is protected with Silicon diodes to limit the

applied voltage. Also, make sure to sequence the applied voltage to ensure negative gate bias is available before

applying the positive drain supply.

App Note [2] Bias Arrangement

-

For Parallel Stage Bias -- The same as Individual Stage Bias but all the drain or gate pad DC bypass capacitors

(~100-200 pF) can be combined. Additional DC bypass capacitance (~0.01 uF) is also recommended to all DC or

combination (if gate or drains are tied together) of DC bias pads.

For Individual Stage Bias -- Each DC pad (Vd1,2 and Vg1,2,3,4) needs to have DC bypass capacitance (~100-200 pF) as

close to the device as possible. Additional DC bypass capacitance (~0.01 uF) is also recommended.

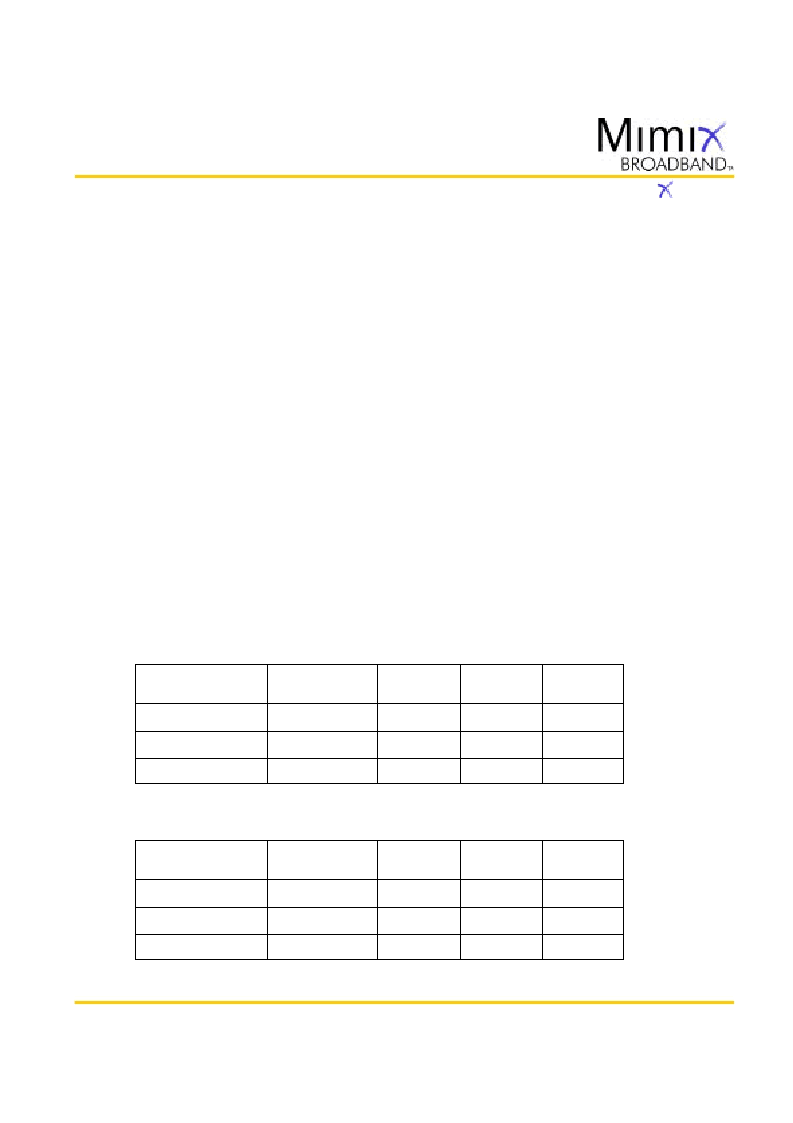

MTTF Tables

Backplate

Temperature

55 deg Celsius

75 deg Celsius

95 deg Celsius

Channel

Temperature

81 deg Celsius

101 deg Celsius

121 deg Celsius

FITs

1.48E-03

2.44E-02

3.04E-01

MTTF Hours

6.77E+11

4.09E+10

3.29E+09

Rth

-

65.0

°

C/W

-

Bias Conditions:

Vd=3.0V, Id=135 mA

Backplate

Temperature

55 deg Celsius

75 deg Celsius

95 deg Celsius

Channel

Temperature

142 deg Celsius

162 deg Celsius

182 deg Celsius

FITs

2.43E+00

1.87E+01

1.20E+02

MTTF Hours

4.11E+08

5.36E+07

8.35E+06

Rth

-

58.9

°

C/W

-

Bias Conditions:

Vd=5.5V, Id=270 mA

These numbers were calculated based on accelerated life test information and thermal model analysis received from the fabricating foundry.

18.0-34.0 GHz GaAs MMIC

Receiver

Mimix Broadband, Inc., 10795 Rockley Rd., Houston, Texas 77099

Tel: 281.988.4600 Fax: 281.988.4615 mimixbroadband.com

Characteristic Data and Specifications are subject to change without notice.

2006 Mimix Broadband, Inc.

Export of this item may require appropriate export licensing from the U.S. Government. In purchasing these parts, U.S. Domestic customers accept

their obligation to be compliant with U.S. Export Laws.

May 2006 - Rev 21-May-06

R1002

相關PDF資料 |

PDF描述 |

|---|---|

| XR1004_06 | 30.0-46.0 GHz GaAs MMIC Receiver |

| XR1004 | 30.0-46.0 GHz GaAs MMIC Receiver |

| XR1005-QD | 19.0-26.0 GHz GaAs Receiver QFN, 7x7 mm |

| XR1005-QD-0N00 | 19.0-26.0 GHz GaAs Receiver QFN, 7x7 mm |

| XR1005-QD-0N0T | 19.0-26.0 GHz GaAs Receiver QFN, 7x7 mm |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XR1002-BD | 制造商:MIMIX 制造商全稱:MIMIX 功能描述:17.65-33.65 GHz GaAs MMIC Receiver |

| XR-1002CN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Filter |

| XR-1002CP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Filter |

| XR1002D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Filter |

| XR1002-QB | 制造商:MIMIX 制造商全稱:MIMIX 功能描述:18.0-30.0 GHz GaAs Receiver QFN, 7x7 mm |

發(fā)布緊急采購,3分鐘左右您將得到回復。