- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375045 > XQ2V3000-4FG456M (Xilinx, Inc.) QPro Virtex-II 1.5V Military QML Platform FPGAs PDF資料下載

參數(shù)資料

| 型號(hào): | XQ2V3000-4FG456M |

| 廠商: | Xilinx, Inc. |

| 英文描述: | QPro Virtex-II 1.5V Military QML Platform FPGAs |

| 中文描述: | QPro的Virtex - II 1.5V的軍事QML第平臺(tái)FPGA |

| 文件頁(yè)數(shù): | 62/128頁(yè) |

| 文件大?。?/td> | 2738K |

| 代理商: | XQ2V3000-4FG456M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)當(dāng)前第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)

QPro Virtex-II 1.5V Military QML Platform FPGAs

62

www.xilinx.com

1-800-255-7778

DS122 (v1.1) January 7, 2004

Product Specification

R

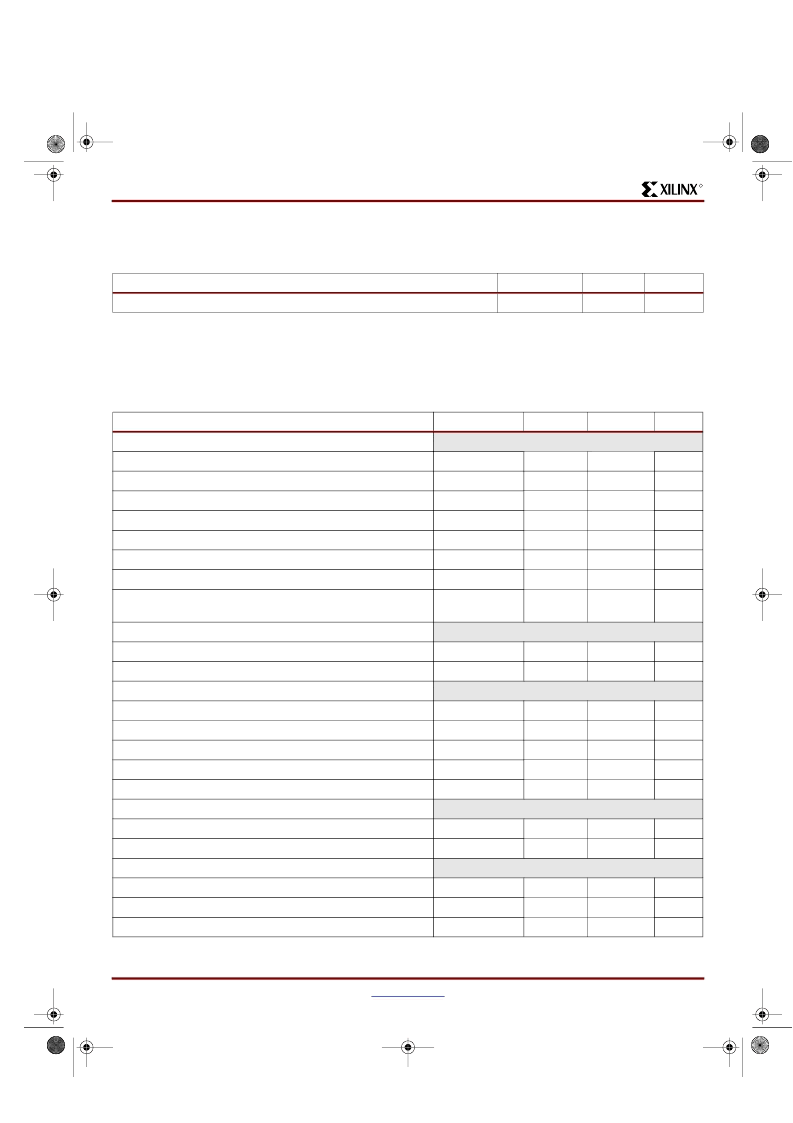

Clock Distribution Switching Characteristics

CLB Switching Characteristics

Delays originating at F/G inputs vary slightly according to the input used (see

Figure 49

). The values listed below are

worst-case. Precise values are provided by the timing analyzer.

Table 48:

Clock Distribution Switching Characteristics

Description

Symbol

Value

Units

Global Clock Buffer I input to O output

T

GIO

0.59

ns

Table 49:

CLB Switching Characteristics

Description

Symbol

Min

Max

Units

Combinatorial Delays

4-input function: F/G inputs to X/Y outputs

T

ILO

T

IF5

T

IF5X

T

IFXY

T

INAFX

T

INBFX

T

SOPSOP

-

0.44

ns

5-input function: F/G inputs to F5 output

-

0.72

ns

5-input function: F/G inputs to X output

-

0.95

ns

FXINA or FXINB inputs to Y output via MUXFX

-

0.45

ns

FXINA input to FX output via MUXFX

-

0.32

ns

FXINB input to FX output via MUXFX

-

0.32

ns

SOPIN input to SOPOUT output via ORCY

-

0.44

ns

Incremental delay routing through transparent latch to XQ/YQ

outputs

T

IFNCTL

-

0.51

ns

Sequential Delays

FF Clock CLK to XQ/YQ outputs

T

CKO

T

CKLO

-

0.57

ns

Latch Clock CLK to XQ/YQ outputs

-

0.68

ns

Setup and Hold Times Before/After Clock CLK

BX/BY inputs

T

DICK

/T

CKDI

T

DYCK

/T

CKDY

T

DXQK

/T

CKDX

T

CECK

/T

CKCE

T

SRCK/

T

SCKR

0.37/–0.09

-

ns

DY inputs

0.37/–0.09

-

ns

DX inputs

0.37/–0.09

-

ns

CE input

0.24/–0.08

-

ns

SR/BY inputs (synchronous)

0.26/–0.03

-

ns

Clock CLK

Minimum Pulse Width, High

T

CH

T

CL

0.77

-

ns

Minimum Pulse Width, Low

0.77

-

ns

Set/Reset

Minimum Pulse Width, SR/BY inputs

T

RPW

T

RQ

F

TOG

0.77

-

ns

Delay from SR/BY inputs to XQ/YQ outputs (asynchronous)

-

1.34

ns

Toggle Frequency (MHz) (for export control)

-

650

MHz

ds122_1_1.fm Page 62 Wednesday, January 7, 2004 9:15 PM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XQ2V3000-4FG456N | QPro Virtex-II 1.5V Military QML Platform FPGAs |

| XQ2V6000 | QPro Virtex-II 1.5V Military QML Platform FPGAs |

| XQ2V6000-4BG575M | QPro Virtex-II 1.5V Military QML Platform FPGAs |

| XQ2V6000-4BG575N | QPro Virtex-II 1.5V Military QML Platform FPGAs |

| XQ2V6000-4BG728M | QPro Virtex-II 1.5V Military QML Platform FPGAs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XQ2V3000-4FG456N | 制造商:XILINX 制造商全稱:XILINX 功能描述:QPro Virtex-II 1.5V Military QML Platform FPGAs |

| XQ2V3000-BG575I | 制造商:XILINX 制造商全稱:XILINX 功能描述:QPro Virtex-II 1.5V Platform FPGAs |

| XQ2V3000-BG575M | 制造商:XILINX 制造商全稱:XILINX 功能描述:QPro Virtex-II 1.5V Platform FPGAs |

| XQ2V3000-BG575N | 制造商:XILINX 制造商全稱:XILINX 功能描述:QPro Virtex-II 1.5V Platform FPGAs |

| XQ2V3000-BG728I | 制造商:XILINX 制造商全稱:XILINX 功能描述:QPro Virtex-II 1.5V Platform FPGAs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。