- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4191 > XCV2000E-8FG1156C (Xilinx Inc)IC FPGA 1.8V C-TEMP 1156-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | XCV2000E-8FG1156C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 201/233頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V C-TEMP 1156-BGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex®-E |

| LAB/CLB數(shù): | 9600 |

| 邏輯元件/單元數(shù): | 43200 |

| RAM 位總計(jì): | 655360 |

| 輸入/輸出數(shù): | 804 |

| 門(mén)數(shù): | 2541952 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 1156-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1156-FBGA(35x35) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)當(dāng)前第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)

2000-2014 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

DS022-2 (v3.0) March 21, 2014

Module 2 of 4

Production Product Specification

1

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Architectural Description

Virtex-E Array

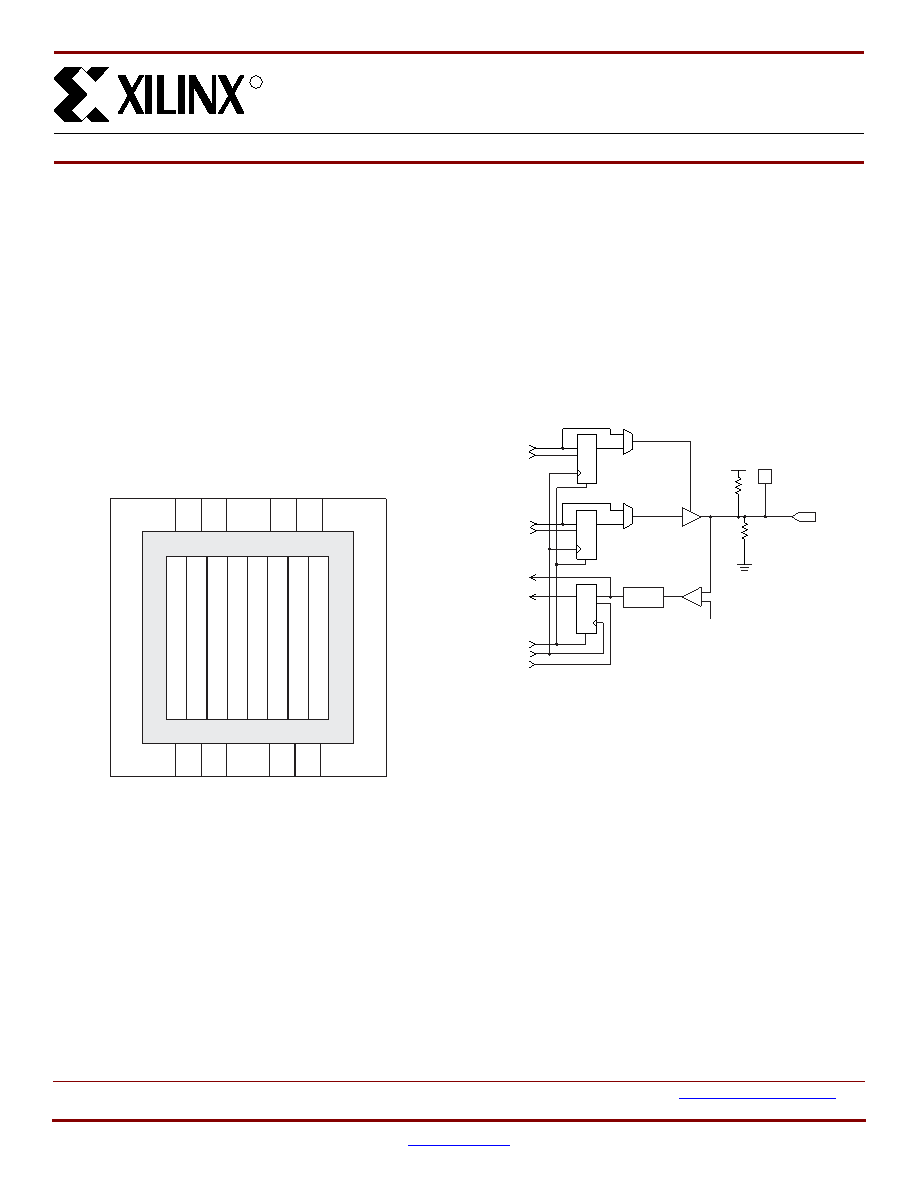

The Virtex-E user-programmable gate array, shown in

Figure 1, comprises two major configurable elements: con-

figurable logic blocks (CLBs) and input/output blocks (IOBs).

CLBs provide the functional elements for constructing

logic

IOBs provide the interface between the package pins

and the CLBs

CLBs interconnect through a general routing matrix (GRM).

The GRM comprises an array of routing switches located at

the intersections of horizontal and vertical routing channels.

Each CLB nests into a VersaBlock that also provides local

routing resources to connect the CLB to the GRM.

The VersaRing I/O interface provides additional routing

resources around the periphery of the device. This routing

improves I/O routability and facilitates pin locking.

The Virtex-E architecture also includes the following circuits

that connect to the GRM.

Dedicated block memories of 4096 bits each

Clock DLLs for clock-distribution delay compensation

and clock domain control

3-State buffers (BUFTs) associated with each CLB that

drive dedicated segmentable horizontal routing

resources

Values stored in static memory cells control the configurable

load into the memory cells on power-up, and can reload if

necessary to change the function of the device.

Input/Output Block

The Virtex-E IOB, Figure 2, features SelectI/O+ inputs and

outputs that support a wide variety of I/O signalling stan-

dards, see Table 1.

The three IOB storage elements function either as

edge-triggered D-type flip-flops or as level-sensitive latches.

Each IOB has a clock signal (CLK) shared by the three

flip-flops and independent clock enable signals for each

flip-flop.

0

Virtex-E 1.8 V

Field Programmable Gate Arrays

DS022-2 (v3.0) March 21, 2014

00

Production Product Specification

R

Figure 1: Virtex-E Architecture Overview

DLLDLL

IOBs

VersaRing

ds022_01_121099

CLBs

BRAMs

CLBs

BRAMs

CLBs

DLLDLL

Figure 2: Virtex-E Input/Output Block (IOB)

OBUFT

IBUF

Vref

ds022_02_091300

SR

CLK

ICE

OCE

O

I

IQ

T

TCE

D

CE

Q

SR

D

CE

Q

SR

D

CE

Q

SR

PAD

Programmable

Delay

Weak

Keeper

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCV2000E-7FG1156I | IC FPGA 1.8V I-TEMP 1156-FBGA |

| HMC50DRYI-S734 | CONN EDGECARD 100PS DIP .100 SLD |

| XC5VTX150T-2FFG1759I | IC FPGA VIRTEX5TXT 150K 1759FBGA |

| XC5VTX150T-2FF1759I | IC FPGA VIRTEX5TXT 150K 1759FBGA |

| ACB60DHAT-S621 | EDGECARD 120POS R/A .050 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV2000E-8FG1156I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Virtex-E 1.8 V Field Programmable Gate Arrays |

| XCV2000E-8FG240C | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Virtex⑩-E 1.8 V Field Programmable Gate Arrays |

| XCV2000E-8FG240I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Virtex⑩-E 1.8 V Field Programmable Gate Arrays |

| XCV2000E-8FG680C | 功能描述:IC FPGA 1.8V C-TEMP 680-FBGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Virtex®-E 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門(mén)數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類(lèi)型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XCV2000E-8FG680I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Virtex-E 1.8 V Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。