- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4144 > XCS05XL-5VQ100C (Xilinx Inc)IC FPGA 3.3V C-TEMP 100-VQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XCS05XL-5VQ100C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 49/83頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 3.3V C-TEMP 100-VQFP |

| 產(chǎn)品變化通告: | Product Discontinuation 26/Oct/2011 |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-XL |

| LAB/CLB數(shù): | 100 |

| 邏輯元件/單元數(shù): | 238 |

| RAM 位總計(jì): | 3200 |

| 輸入/輸出數(shù): | 77 |

| 門數(shù): | 5000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)當(dāng)前第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)

Spartan and Spartan-XL FPGA Families Data Sheet

DS060 (v2.0) March 1, 2013

53

Product Specification

R

Product Obsolete/Under Obsolescence

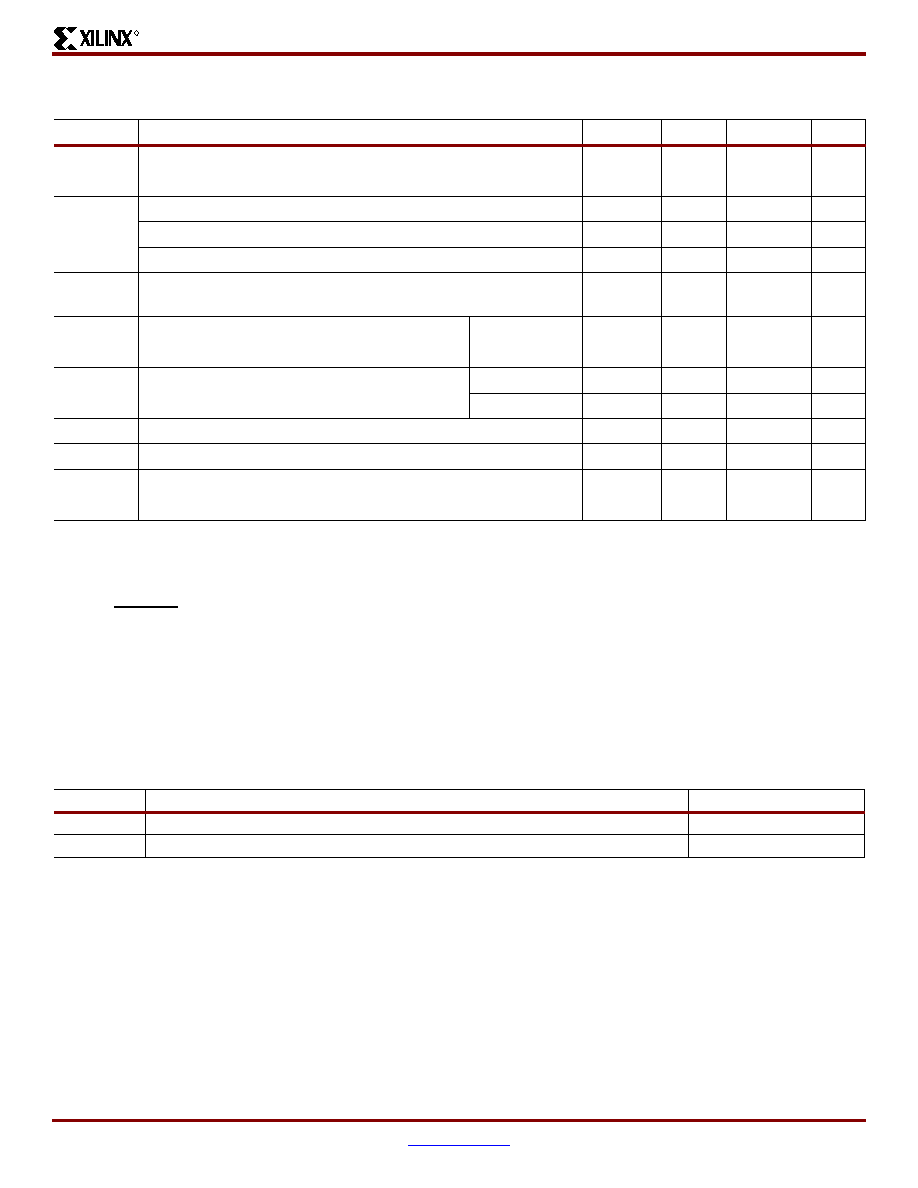

Spartan-XL Family DC Characteristics Over Operating Conditions

Supply Current Requirements During Power-On

Spartan-XL FPGAs require that a minimum supply current

ICCPO be provided to the VCC lines for a successful power

on. If more current is available, the FPGA can consume

more than ICCPO min., though this cannot adversely affect

reliability.

A maximum limit for ICCPO is not specified. Be careful when

using foldback/crowbar supplies and fuses. It is possible to

control the magnitude of ICCPO by limiting the supply current

available to the FPGA. A current limit below the trip level will

avoid inadvertently activating over-current protection cir-

cuits.

Symbol

Description

Min

Typ.

Max

Units

VOH

High-level output voltage @ IOH = –4.0 mA, VCC min (LVTTL)

2.4

-

V

High-level output voltage @ IOH = –500 μA, (LVCMOS)

90% VCC

--

V

VOL

Low-level output voltage @ IOL = 12.0 mA, VCC min (LVTTL)(1)

--

0.4

V

Low-level output voltage @ IOL = 24.0 mA, VCC min (LVTTL)(2)

--

0.4

V

Low-level output voltage @ IOL = 1500 μA, (LVCMOS)

-

10% VCC

V

VDR

Data retention supply voltage (below which configuration data

may be lost)

2.5

-

V

ICCO

Quiescent FPGA supply current(3,4)

Commercial

-

0.1

2.5

mA

Industrial

-

0.1

5

mA

ICCPD

Power Down FPGA supply current(3,5)

Commercial

-

0.1

2.5

mA

Industrial

-

0.1

5

mA

IL

Input or output leakage current

–10

-

10

μA

CIN

Input capacitance (sample tested)

-

10

pF

IRPU

Pad pull-up (when selected) @ VIN = 0V (sample tested)

0.02

-

0.25

mA

IRPD

Pad pull-down (when selected) @ VIN = 3.3V (sample tested)

0.02

-

mA

Notes:

1.

With up to 64 pins simultaneously sinking 12 mA (default mode).

2.

With up to 64 pins simultaneously sinking 24 mA (with 24 mA option selected).

3.

With 5V tolerance not selected, no internal oscillators, and the FPGA configured with the Tie option.

4.

With no output current loads, no active input resistors, and all package pins at VCC or GND.

5.

With PWRDWN active.

Symbol

Description

Min

Max

Units

ICCPO

Total VCC supply current required during power-on

100

-

mA

TCCPO

VCC ramp time(2,3)

-50

ms

Notes:

1.

The ICCPO requirement applies for a brief time (commonly only a few milliseconds) when VCC ramps from 0 to 3.3V.

2.

The ramp time is measured from GND to VCC max on a fully loaded board.

3.

VCC must not dip in the negative direction during power on.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCS05XL-5PC84C | IC FPGA 3.3V C-TEMP 84-PLCC |

| 65801-032LF | CLINCHER RECEPTACLE ASSY TIN |

| IDT71V321S55TF8 | IC SRAM 16KBIT 55NS 64STQFP |

| IDT71321SA55TF8 | IC SRAM 16KBIT 55NS 64STQFP |

| IDT7140SA35PF8 | IC SRAM 8KBIT 35NS 64TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS05XL-5VQ100I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL FPGA |

| XCS05XL-5VQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-5VQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-5VQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-5VQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。