- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375007 > XCF08PVO48 (Xilinx, Inc.) Platform Flash In-System Programmable Configuration PROMS PDF資料下載

參數(shù)資料

| 型號: | XCF08PVO48 |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Platform Flash In-System Programmable Configuration PROMS |

| 中文描述: | 平臺Flash在系統(tǒng)可編程配置方案管理系統(tǒng) |

| 文件頁數(shù): | 36/46頁 |

| 文件大?。?/td> | 525K |

| 代理商: | XCF08PVO48 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

Platform Flash In-System Programmable Configuration PROMS

DS123 (v2.9) May 09, 2006

www.xilinx.com

36

R

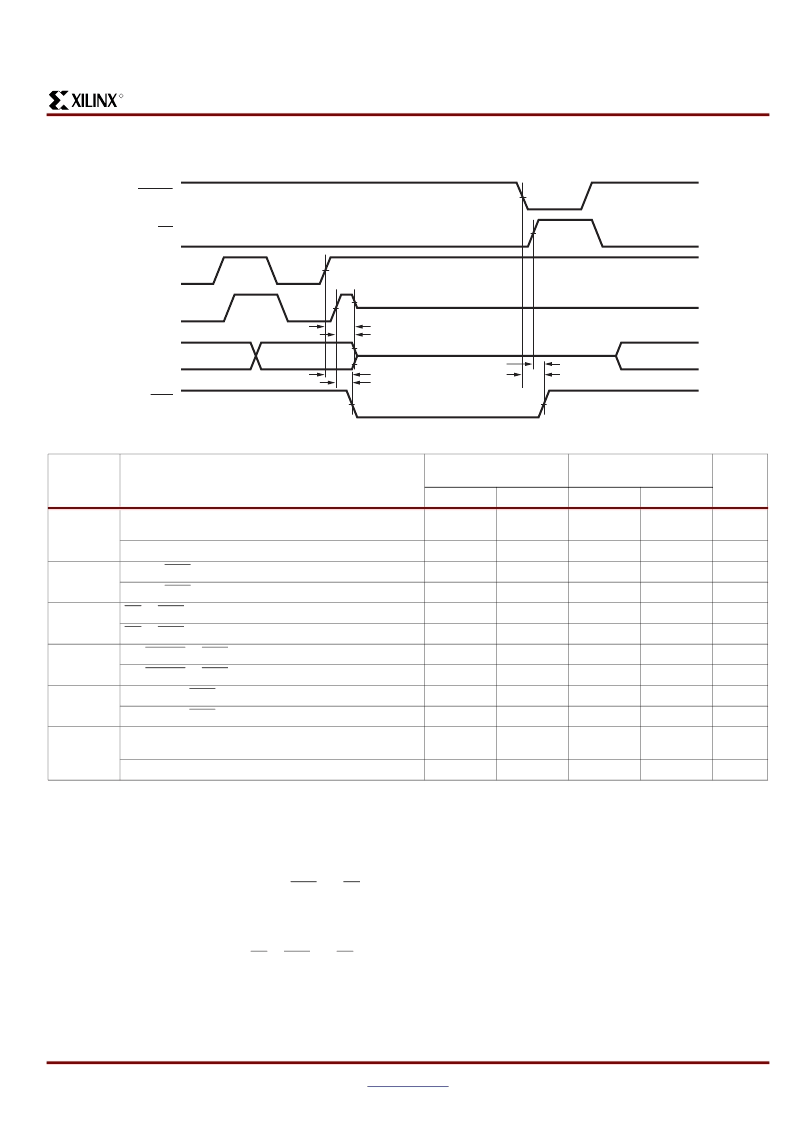

AC Characteristics Over Operating Conditions When Cascading

Symbol

Description

XCF01S, XCF02S,

XCF04S

XCF08P, XCF16P,

XCF32P

Units

Min

Max

Min

Max

T

CDF

CLK to output float delay

(2,3)

when V

CCO

= 2.5V or 3.3V

CLK to output float delay

(2,3)

when V

CCO

= 1.8V

CLK to CEO delay

(3,5)

when V

CCO

= 2.5V or 3.3V

CLK to CEO delay

(3,5)

when V

CCO

= 1.8V

CE to CEO delay

(3,6)

when V

CCO

= 2.5V or 3.3V

CE to CEO delay

(3,6)

when V

CCO

= 1.8V

OE/RESET to CEO delay

(3)

when V

CCO

= 2.5V or 3.3V

OE/RESET to CEO delay

(3)

when V

CCO

= 1.8V

CLKOUT to CEO delay when V

CCO

= 2.5V or 3.3V

CLKOUT to CEO delay when V

CCO

= 1.8V

CLKOUT to output float delay

when V

CCO

= 2.5V or 3.3V

CLKOUT to output float delay when V

CCO

= 1.8V

–

25

–

20

ns

–

35

–

20

ns

T

OCK

–

20

–

20

ns

–

35

–

20

ns

T

OCE

–

20

–

80

ns

–

35

–

80

ns

T

OOE

–

20

–

80

ns

–

35

–

80

ns

T

COCE

–

–

–

20

ns

–

–

–

20

ns

T

CODF

–

–

–

25

ns

–

–

–

25

ns

Notes:

1.

2.

3.

4.

5.

AC test load = 50 pF for XCF01S/XCF02S/XCF04S; 30 pF for XCF08P/XCF16P/XCF32P.

Float delays are measured with 5 pF AC loads. Transition is measured at ±200 mV from steady state active levels.

Guaranteed by design, not tested.

All AC parameters are measured with V

IL

= 0.0V and V

IH

= 3.0V.

For cascaded PROMs, if the FPGA’s dual-purpose configuration data pins are set to persist as configuration pins, the minimum

period is increased based on the CLK to CEO and CE to data propagation delays:

- T

CYC

minimum = T

OCK

+ T

CE

+ FPGA Data setup time.

- T

CAC

maximum = T

OCK

+ T

CE

For cascaded PROMs, if the FPGA’s dual-purpose configuration data pins become general I/O pins after configuration; to allow for

the disable to propagate to the cascaded PROMs and to avoid contention on the data lines following configuration, the minimum

period is increased based on the CE to CEO and CE to data propagation delays:

- T

CYC

minimum = T

OCE

+ T

CE

- T

CAC

maximum = T

OCK

+ T

CE

6.

OE/RESET

CE

CLK

CLKOUT

(optional)

DATA

CEO

T

OCE

T

OOE

First Bit

Last Bit

T

CDF

T

CODF

T

OCK

T

COCE

ds123_23_102203

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCF08PVO48C | Platform Flash In-System Programmable Configuration PROMS |

| XCF08PVOG48 | Platform Flash In-System Programmable Configuration PROMS |

| XCF08PVOG48C | Platform Flash In-System Programmable Configuration PROMS |

| XCF16P | Platform Flash In-System Programmable Configuration PROMS |

| XCF16PF48 | Platform Flash In-System Programmable Configuration PROMS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCF08PVO48C | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XCF08PVO48C | 制造商:Xilinx 功能描述: |

| XCF08PVO48C0973 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XCF08PVO48CES | 制造商:Xilinx 功能描述: |

| XCF08PVO48CESB | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。