- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4187 > XC5VLX330T-2FF1738C (Xilinx Inc)IC FPGA VIRTEX-5 330K 1738FBGA PDF資料下載

參數(shù)資料

| 型號: | XC5VLX330T-2FF1738C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 49/91頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA VIRTEX-5 330K 1738FBGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex®-5 LXT |

| LAB/CLB數(shù): | 25920 |

| 邏輯元件/單元數(shù): | 331776 |

| RAM 位總計: | 11943936 |

| 輸入/輸出數(shù): | 960 |

| 電源電壓: | 0.95 V ~ 1.05 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 1738-BBGA,F(xiàn)CBGA |

| 供應(yīng)商設(shè)備封裝: | 1738-FCBGA |

| 配用: | 568-5088-ND - BOARD DEMO DAC1408D750 HW-V5-ML525-FXT-UNI-G-J-ND - EVAL BD ROCKETIO GTX VIRTEX5 JPN HW-V5-ML525-FXT-UNI-G-ND - EVAL BOARD ROCKETIO GTX VIRTEX5 HW-V5-ML525-UNI-G-ND - EVAL PLATFORM ROCKET IO VIRTEX-5 HW-AFX-FF1738-500-G-ND - BOARD DEV VIRTEX 5 FF1738 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁

Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

DS202 (v5.3) May 5, 2010

Product Specification

53

Clock Buffers and Networks

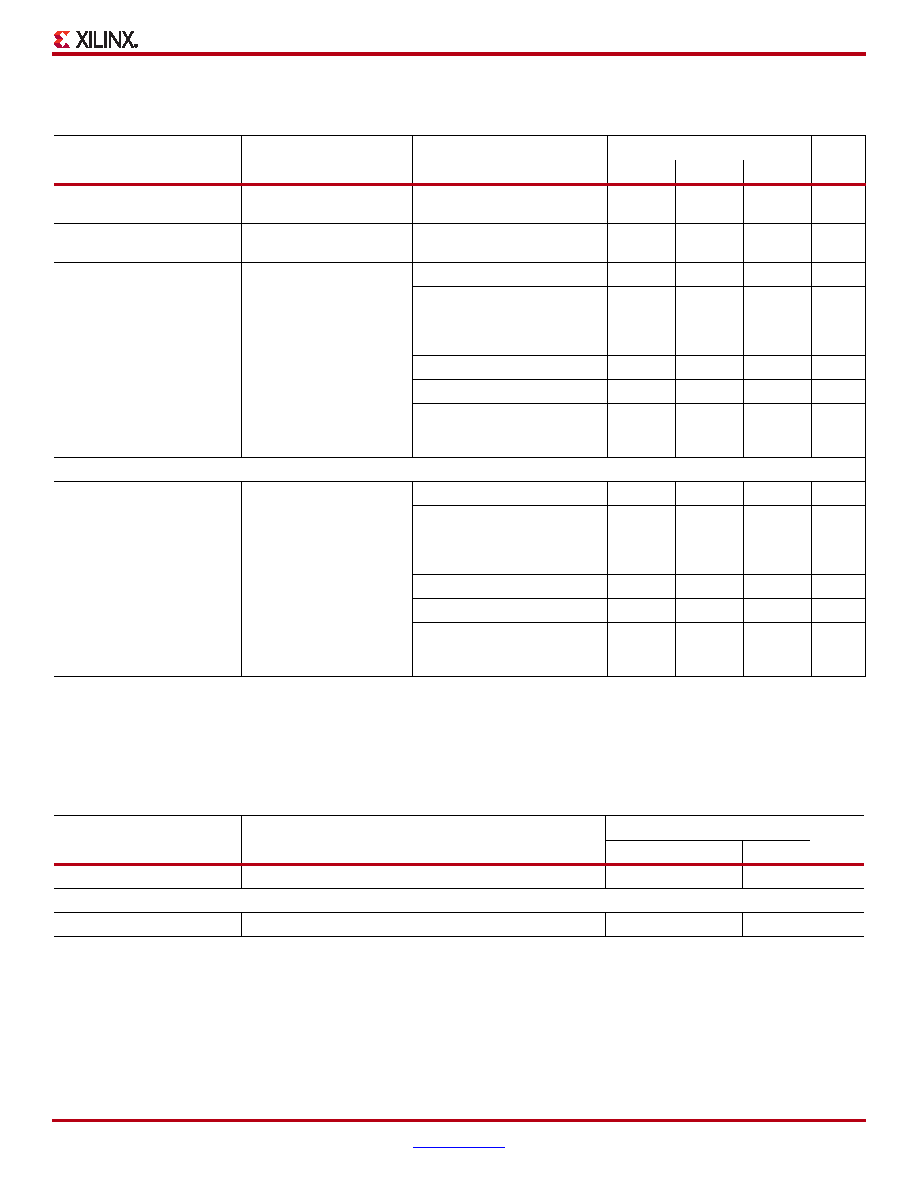

Table 71: Global Clock Switching Characteristics (Including BUFGCTRL)

Symbol

Description

Devices

Speed Grade

Units

-3

-2

-1

TBCCCK_CE/TBCCKC_CE(1)

CE pins Setup/Hold

All

0.27

0.00

0.27

0.00

0.31

0.00

ns

TBCCCK_S/TBCCKC_S(1)

S pins Setup/Hold

All

0.27

0.00

0.27

0.00

0.31

0.00

ns

TBCCKO_O(2)

BUFGCTRL delay from

I0/I1 to O

LX20T

N/A

0.24

0.30

ns

LX30, LX30T, LX50, LX50T,

LX85, LX85T, LX110, LX110T,

SX35T, SX50T, FX70T,

FX100T, and FX130T

0.19

0.22

0.25

ns

FX30T

0.23

0.25

ns

LX155 and LX155T

0.12

0.14

0.30

ns

LX220, LX220T, LX330,

LX330T, SX95T, SX240T,

TX150T, TX240T, and FX200T

N/A

0.22

0.25

ns

Maximum Frequency

FMAX

Global clock tree (BUFG)

LX20T

N/A

667

600

MHz

LX30, LX30T, LX50, LX50T,

LX85, LX85T, LX110, LX110T,

SX35T, SX50T, FX30T, and

FX70T

710

667

600

MHz

LX155, LX155T, and FX100T

650

600

550

MHz

FX130T

550

500

450

MHz

LX220, LX220T, LX330,

LX330T, SX95T, SX240T,

TX150T, TX240T, and FX200T

N/A

500

450

MHz

Notes:

1.

TBCCCK_CE and TBCCKC_CE must be satisfied to assure glitch-free operation of the global clock when switching between clocks. These

parameters do not apply to the BUFGMUX_VIRTEX4 primitive that assures glitch-free operation. The other global clock setup and hold times

are optional; only needing to be satisfied if device operation requires simulation matches on a cycle-for-cycle basis when switching between

clocks.

2.

TBGCKO_O (BUFG delay from I0 to O) values are the same as TBCCKO_O values.

Table 72: Input/Output Clock Switching Characteristics (BUFIO)

Symbol

Description

Speed Grade

Units

-3

-2

-1

TBUFIOCKO_O

Clock to out delay from I to O

1.08

1.16

1.29

ns

Maximum Frequency

FMAX

I/O clock tree (BUFIO)

710

644

MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC6VSX475T-2FFG1759E | IC FPGA VIRTEX 1759FCBGA |

| XC6VSX475T-L1FF1759I | IC FPGA VIRTEX-6SXT 1759FFBGA |

| RSC65DRAS | CONN EDGECARD 130PS R/A .100 SLD |

| XC6VLX760-L1FFG1760C | IC FPGA VIRTEX 6 758K 1760FFGBGA |

| RMC65DRAS | CONN EDGECARD 130PS R/A .100 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5VLX330T-2FF1738CES | 制造商:Xilinx 功能描述: |

| XC5VLX330T-2FFG1738C | 功能描述:IC FPGA VIRTEX-5 330K 1738FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Virtex®-5 LXT 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC5VLX330T-2FFG1738CES | 制造商:Xilinx 功能描述: |

| XC5VLX330T-2FFG1738CES9993 | 制造商:Xilinx 功能描述: |

| XC5VLX50 | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-5 Family Overview |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。