- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4173 > XC5210-5PQ208C (Xilinx Inc)IC FPGA 324 CLB'S 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC5210-5PQ208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 31/73頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 324 CLB'S 208-PQFP |

| 產(chǎn)品變化通告: | XC1700 PROMs,XC5200,HQ,SCD Parts Discontinuation 19/Jul/2010 |

| 標準包裝: | 24 |

| 系列: | XC5200 |

| LAB/CLB數(shù): | 324 |

| 邏輯元件/單元數(shù): | 1296 |

| 輸入/輸出數(shù): | 164 |

| 門數(shù): | 16000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應商設備封裝: | 208-PQFP(28x28) |

| 其它名稱: | 122-1148 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

November 5, 1998 (Version 5.2)

7-119

XC5200 Series Field Programmable Gate Arrays

7

Notes:

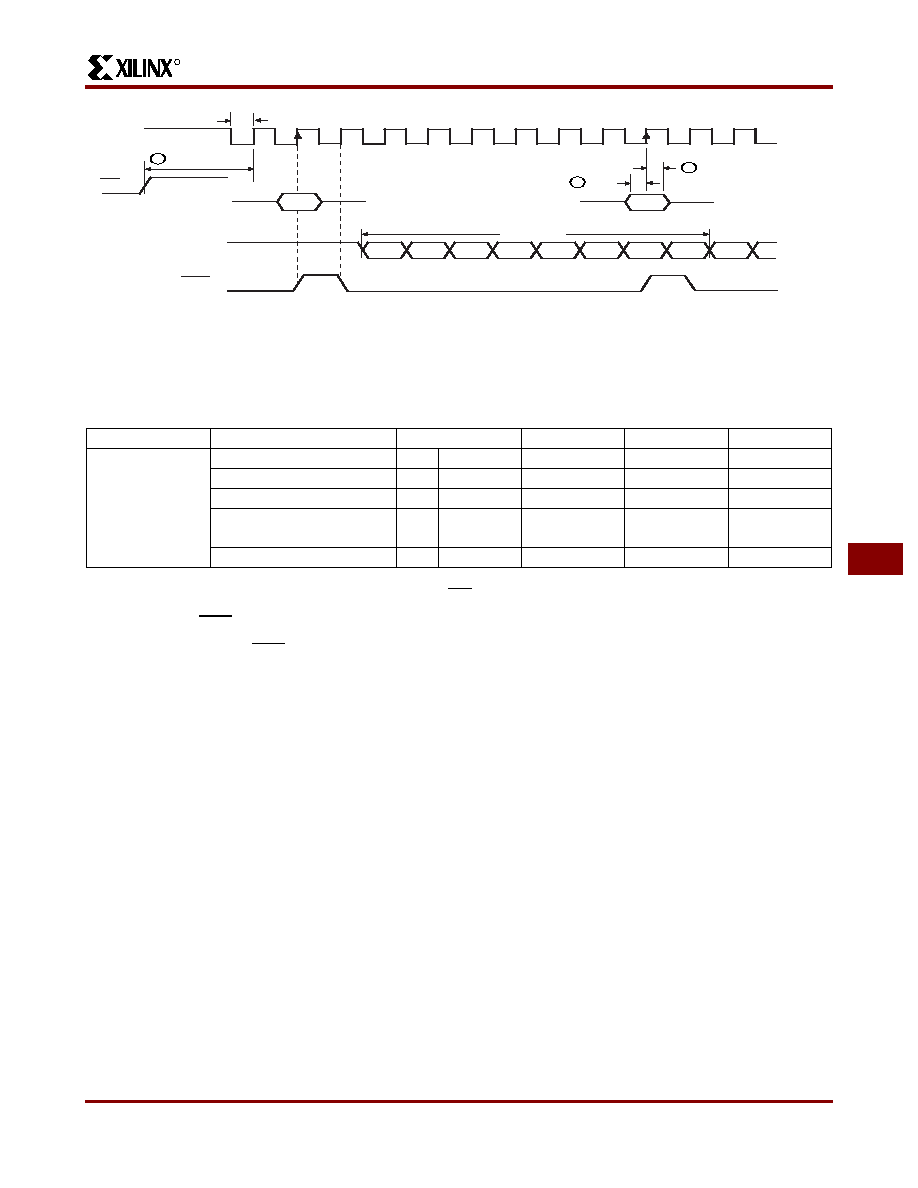

1. Peripheral Synchronous mode can be considered Slave Parallel mode. An external CCLK provides timing, clocking in the

first data byte on the second rising edge of CCLK after INIT goes high. Subsequent data bytes are clocked in on every

eighth consecutive rising edge of CCLK.

2. The RDY/BUSY line goes High for one CCLK period after data has been clocked in, although synchronous operation does

not require such a response.

3. The pin name RDY/BUSY is a misnomer. In synchronous peripheral mode this is really an ACKNOWLEDGE signal.

4.Note that data starts to shift out serially on the DOUT pin 0.5 CCLK periods after it was loaded in parallel. Therefore,

additional CCLK pulses are clearly required after the last byte has been loaded.

Figure 34: Synchronous Peripheral Mode Programming Switching Characteristics

0

DOUT

CCLK

1

2

345

6

7

BYTE

0

BYTE

1

BYTE 0 OUT

BYTE 1 OUT

RDY/BUSY

INIT

1

0

X6096

TCCL

D0 - D7

TIC

TCD

TDC

1

2

3

Description

Symbol

Min

Max

Units

CCLK

INIT (High) setup time

1

TIC

5

s

D0 - D7 setup time

2

TDC

60

ns

D0 - D7 hold time

3

TCD

0ns

CCLK High time

TCCH

50

ns

CCLK Low time

TCCL

60

ns

CCLK Frequency

FCC

8MHz

Product Obsolete or Under Obsolescence

相關PDF資料 |

PDF描述 |

|---|---|

| ASC43DRAI-S734 | CONN EDGECARD 86POS .100 R/A PCB |

| XC5210-6PQ160C | IC FPGA 324 CLB'S 160-PQFP |

| XC5210-4PQ160C | IC FPGA 324 CLB'S 160-PQFP |

| XC5204-6PQ160C | IC FPGA 120 CLB'S 160-PQFP |

| ACB66DHAN-S621 | EDGECARD 132POS DIP R/A .050 SLD |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5210-5PQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5210-5PQ240C | 功能描述:IC FPGA 324 CLB'S 240-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:XC5200 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應商設備封裝:120-CPGA(34.55x34.55) |

| XC5210-5PQ240C0167 | 制造商:Xilinx 功能描述: |

| XC5210-5PQ240I | 制造商:Xilinx 功能描述: |

| XC5210-5PQG208C | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。