- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4173 > XC3030L-8VQ64C (Xilinx Inc)IC FPGA C-TEMP 3.3V 64-VQFP PDF資料下載

參數(shù)資料

| 型號: | XC3030L-8VQ64C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 62/76頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA C-TEMP 3.3V 64-VQFP |

| 產(chǎn)品變化通告: | XC3000(L) Discontinuation 01/Feb/2003 |

| 標(biāo)準(zhǔn)包裝: | 64 |

| 系列: | XC3000A/L |

| LAB/CLB數(shù): | 100 |

| RAM 位總計(jì): | 22176 |

| 輸入/輸出數(shù): | 54 |

| 門數(shù): | 2000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 64-TQFP |

| 供應(yīng)商設(shè)備封裝: | 64-VQFP(10x10) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁當(dāng)前第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

R

November 9, 1998 (Version 3.1)

7-67

XC3000 Series Field Programmable Gate Arrays

7

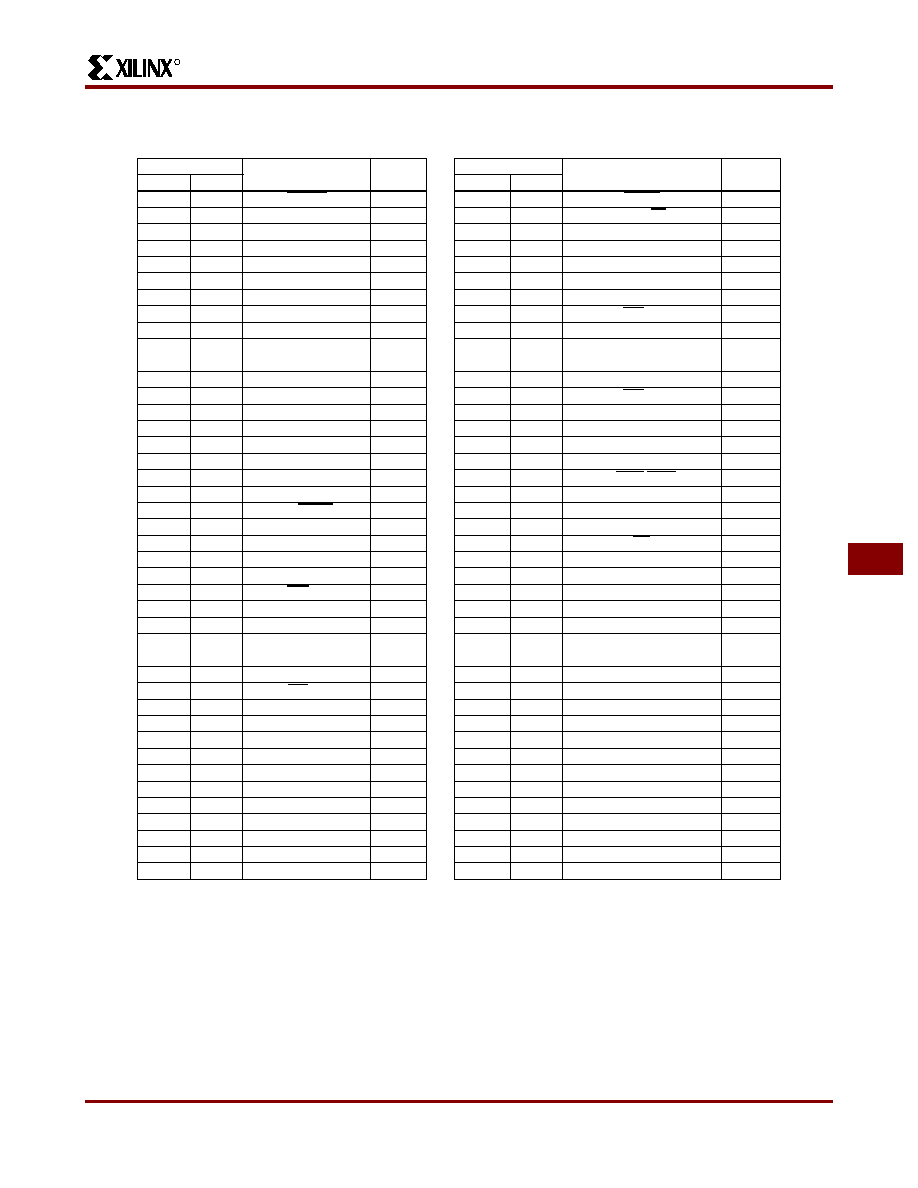

XC3000 Series 68-Pin PLCC, 84-Pin PLCC and PGA Pinouts

XC3000A, XC3000L, XC3100A, and XC3100L families have identical pinouts

Unprogrammed IOBs have a default pull-up. This prevents an undefined pad level for unbonded or unused IOBs.

Programmed outputs are default slew-rate limited.

This table describes the pinouts of three different chips in three different packages. The pin-description column lists 84 of the

118 pads on the XC3042A (and 84 of the 98 pads on the XC3030A) that are connected to the 84 package pins. Ten pads,

indicated by an asterisk, do not exist on the XC3020A, which has 74 pads; therefore the corresponding pins on the 84-pin

packages have no connections to an XC3020A. Six pads on the XC3020A and 16 pads on the XC3030A, indicated by a

dash (—) in the 68 PLCC column, have no connection to the 68 PLCC, but are connected to the 84-pin packages.

68 PLCC

XC3020A, XC3030A,

XC3042A

84 PLCC

68 PLCC

XC3020A, XC3030A,

XC3042A

84 PLCC

XC3030A XC3020A

10

PWRDN

12

44

RESET

54

11

TCLKIN-I/O

13

45

DONE-PG

55

12

—

I/O*

14

46

D7-I/O

56

13

12

I/O

15

47

XTL1(OUT)-BCLKIN-I/O

57

14

13

I/O

16

48

D6-I/O

58

—

I/O

17

—

I/O

59

15

14

I/O

18

49

D5-I/O

60

16

15

I/O

19

50

CS0-I/O

61

—

16

I/O

20

51

D4-I/O

62

17

I/O

21

—

I/O

63

18

VCC

22

52

VCC

64

19

I/O

23

53

D3-I/O

65

—

I/O

24

54

CS1-I/O

66

20

I/O

25

55

D2-I/O

67

—

21

I/O

26

—

I/O

68

21

22

I/O

27

—

I/O*

69

22

—

I/O

28

56

D1-I/O

70

23

I/O

29

57

RDY/BUSY-RCLK-I/O

71

24

I/O

30

58

D0-DIN-I/O

72

25

M1-RDATA

31

59

DOUT-I/O

73

26

M0-RTRIG

32

60

CCLK

74

27

M2-I/O

33

61

A0-WS-I/O

75

28

HDC-I/O

34

62

A1-CS2-I/O

76

29

I/O

35

63

A2-I/O

77

30

LDC-I/O

36

64

A3-I/O

78

—

31

I/O

37

—

I/O*

79

—

I/O*

38

—

I/O*

80

31

32

I/O

39

65

A15-I/O

81

32

33

I/O

40

66

A4-I/O

82

33

—

I/O*

41

67

A14-I/O

83

34

INIT-I/O

42

68

A5-I/O

84

35

GND

43

1

GND

1

36

I/O

44

2

A13-I/O

2

37

I/O

45

3

A6-I/O

3

38

I/O

46

4

A12-I/O

4

39

I/O

47

5

A7-I/O

5

—

40

I/O

48

—

I/O*

6

—

41

I/O

49

—

I/O*

7

40

I/O*

50

6

A11-I/O

8

41

I/O*

51

7

A8-I/O

9

42

I/O

52

8

A10-I/O

10

43

XTL2(IN)-I/O

53

9

A9-I/O

11

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S30-5PQ208I | IC FPGA 2.5V I-TEMP 208-PQFP |

| XC2S30-5PQ208C | IC FPGA 2.5V 216 CLB'S 208-PQFP |

| XC2S15-6CS144C | IC FPGA 2.5V C-TEMP 144-CSBGA |

| XC2S15-5CS144I | IC FPGA 2.5V I-TEMP 144-CSBGA |

| XC2S15-5CS144C | IC FPGA 2.5V C-TEMP 144-CSBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3030L-8VQ64I | 功能描述:IC FPGA I-TEMP 3.3V 64-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:XC3000A/L 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC3042 | 制造商:Xilinx 功能描述: |

| XC3042-100CB100B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC3042-100CB100C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC3042-100CB100M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。