- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄21986 > XC2S200-5PQG208I (Xilinx Inc)IC SPARTAN-II FPGA 200K 208-PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S200-5PQG208I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 6/99頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC SPARTAN-II FPGA 200K 208-PQFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 1176 |

| 邏輯元件/單元數(shù): | 5292 |

| RAM 位總計(jì): | 57344 |

| 輸入/輸出數(shù): | 140 |

| 門數(shù): | 200000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 產(chǎn)品目錄頁面: | 599 (CN2011-ZH PDF) |

| 其它名稱: | 122-1315 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

14

R

Boundary-scan operation is independent of individual IOB

configurations, and unaffected by package type. All IOBs,

including unbonded ones, are treated as independent

3-state bidirectional pins in a single scan chain. Retention of

the bidirectional test capability after configuration facilitates

the testing of external interconnections.

Table 7 lists the boundary-scan instructions supported in

Spartan-II FPGAs. Internal signals can be captured during

EXTEST by connecting them to unbonded or unused IOBs.

They may also be connected to the unused outputs of IOBs

defined as unidirectional input pins.

The public boundary-scan instructions are available prior to

configuration. After configuration, the public instructions

remain available together with any USERCODE

instructions installed during the configuration. While the

SAMPLE and BYPASS instructions are available during

configuration, it is recommended that boundary-scan

operations not be performed during this transitional period.

In addition to the test instructions outlined above, the

boundary-scan circuitry can be used to configure the FPGA,

and also to read back the configuration data.

To facilitate internal scan chains, the User Register

provides three outputs (Reset, Update, and Shift) that

represent the corresponding states in the boundary-scan

internal state machine.

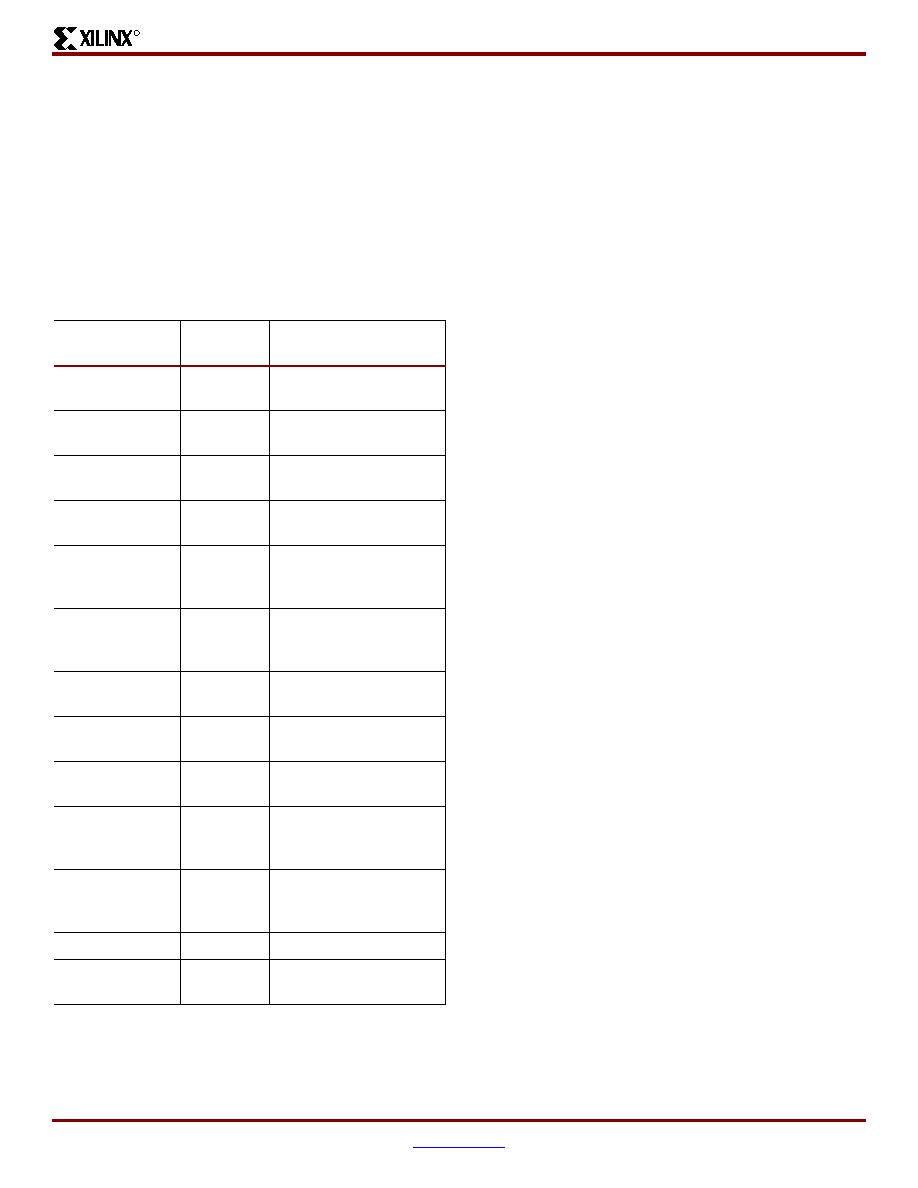

Table 7: Boundary-Scan Instructions

Boundary-Scan

Command

Binary

Code[4:0]

Description

EXTEST

00000

Enables boundary-scan

EXTEST operation

SAMPLE

00001

Enables boundary-scan

SAMPLE operation

USR1

00010

Access user-defined

register 1

USR2

00011

Access user-defined

register 2

CFG_OUT

00100

Access the

configuration bus for

Readback

CFG_IN

00101

Access the

configuration bus for

Configuration

INTEST

00111

Enables boundary-scan

INTEST operation

USRCODE

01000

Enables shifting out

USER code

IDCODE

01001

Enables shifting out of

ID Code

HIZ

01010

Disables output pins

while enabling the

Bypass Register

JSTART

01100

Clock the start-up

sequence when

StartupClk is TCK

BYPASS

11111

Enables BYPASS

RESERVED

All other

codes

Xilinx reserved

instructions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RCB66DHAD-S621 | EDGECARD 132POS DIP R/A .050 SLD |

| RSC43DRYI-S13 | CONN EDGECARD 86POS .100 EXTEND |

| DEM09P500M | CONN DSUB PLUG 9 POS R/A GOLD |

| AIMC-0805-39NJ-T | INDUCTOR MULTILAYER 39NH 0805 |

| RMC43DRYI-S13 | CONN EDGECARD 86POS .100 EXTEND |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S200-5TQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II 2.5V FPGA Family:Introduction and Ordering Information |

| XC2S200-5TQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II 2.5V FPGA Family:Introduction and Ordering Information |

| XC2S200-5TQG144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S200-5TQG144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S200-5VQ100C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II 2.5V FPGA Family:Introduction and Ordering Information |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。