March 2007

Rev. 2

W7NCF-H-M1 Series

5

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

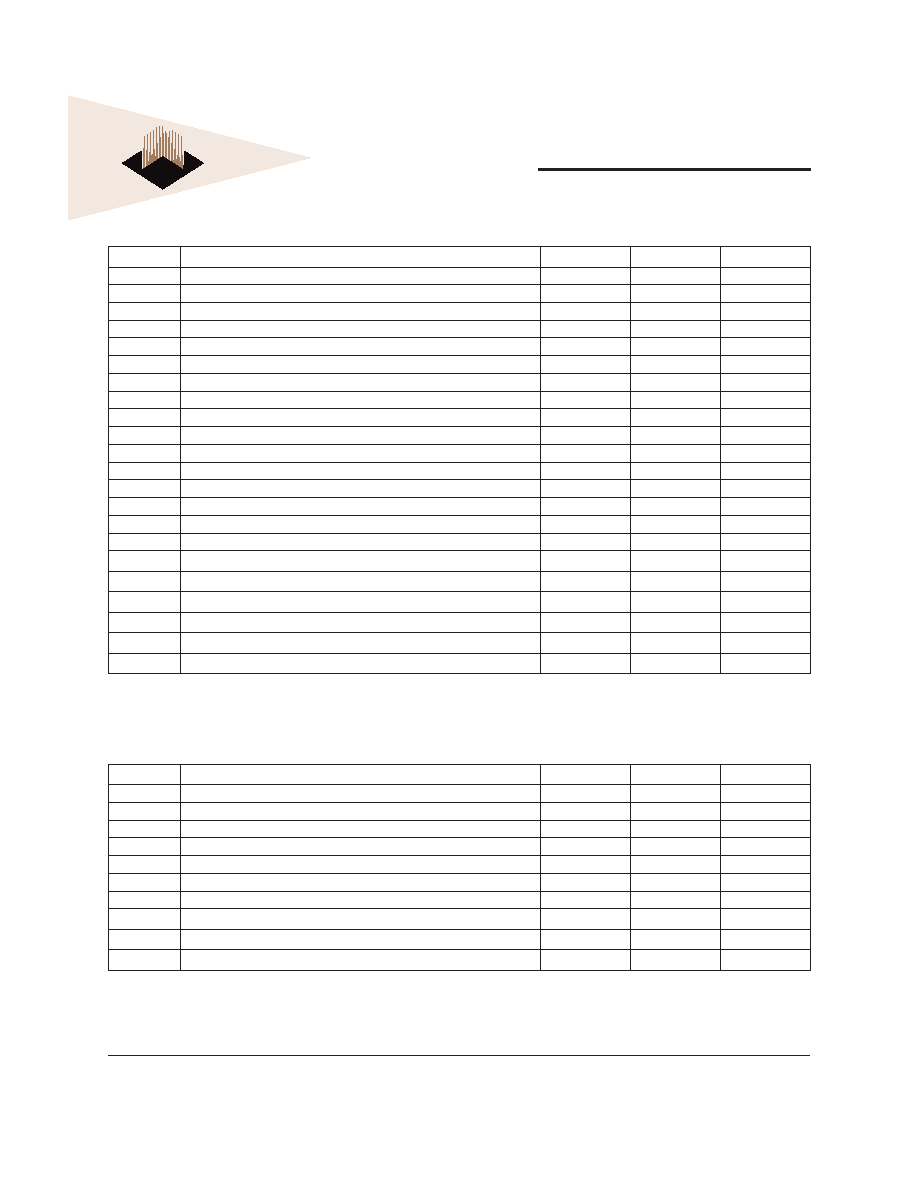

I/O Access Read and Write AC Characteristic

Symbol

Parameter

Min

Max

Units

td(IORD)

Data Delay after IORD

100

ns

th(IORD)

Data Hold following IORD

0

ns

tw(IORD)

IORD pulse width

165

ns

tsuA(IORD)

Address setup time for IORD

70

ns

thA(IORD)

Address hold time for IORD

20

ns

tsuCE(IORD)

Card Enable setup time for IORD

5

ns

thCE(IORD)

Card Enable hold time from IORD

20

ns

tsuREG(IORD)

REG setup time for IORD

5

ns

thREG(IORD)

REG Hold time from IORD

0

ns

tdNP(IORD)

INPACK delay falling from IORD

0

45

ns

tdrlNP(IORD)

INPACK delay rising from IORD

45

ns

tdO16(IORD)

IOIS16 delay falling from address

35

ns

tdrlO16(IORD)

IOIS16 delay rising from address

35

ns

tsu(IOWR)

Data setup time for IOWR

60

ns

th(IOWR)

Data hold time from IOWR

30

ns

tw(IOWR)

IOWR pulse width

165

ns

tsuA(IOWR)

Address setup time for IOWR

70

ns

thA(IOWR)

Address hold time from IOWR

20

ns

tsuCE(IOWR)

Card Enable setup time fro IOWR

5

ns

thCE(IOWR)

Card Enable hold time from IOWR

20

ns

tsuREG(IOWR)

REG setup time for IOWR

5

ns

thREG(IOWR)

REG hold tme from IOWR

0

ns

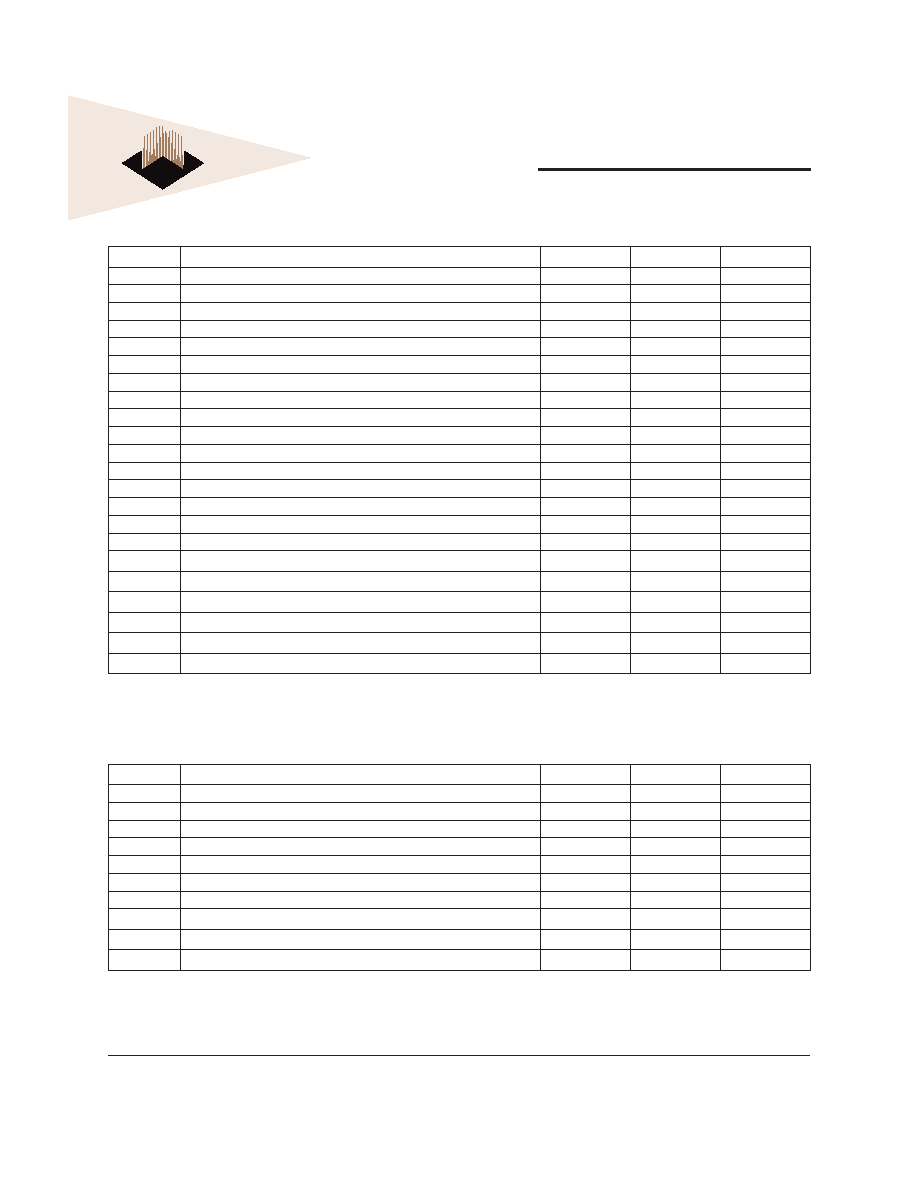

True-IDE Mode I/O Access Read and Write AC Characteristics

Symbol

Parameter

Min

Max

Units

tcR

Cycle time

120

ns

tsuA

Address setup time for IORD/IOWR

25

ns

thA

Address hold time from IORD/IOWR

10

ns

tw

IORD/IORW pulse width

70

ns

trec

IORD/IORW recovery time

25

ns

tsuD(IORD)

Data setup time for IORD

20

ns

thD(IORD)

Data hold time for IORD

5

ns

tdis(IORD)

Output disable time from IORD

30

ns

tsuD(IOWR)

Data setup time for IOWR

20

ns

thD(IOWR)

Data hold following IOWR

10

ns