- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361756 > W.A.R.P.1.1 WEIGHT ASSOCIATIVE RULE PROCESSOR PDF資料下載

參數(shù)資料

| 型號: | W.A.R.P.1.1 |

| 英文描述: | WEIGHT ASSOCIATIVE RULE PROCESSOR |

| 中文描述: | 重量的聯(lián)想規(guī)則處理器 |

| 文件頁數(shù): | 1/28頁 |

| 文件大小: | 275K |

| 代理商: | W.A.R.P.1.1 |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

March 1996

This is advance informationon a new productnow in developmentor undergoingevaluation. Detailsare subject to change without notice.

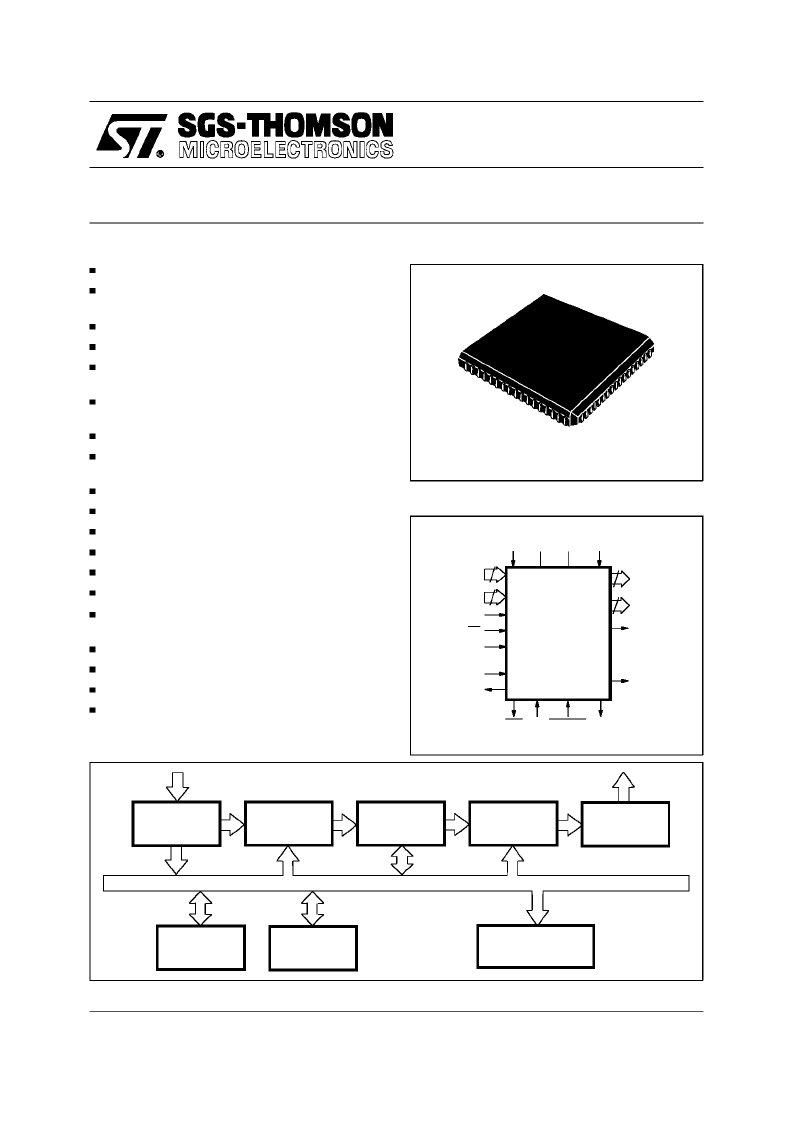

PLCC68

8

I0-I7

BUSY

OFL

12

O0-O11

2

OC0-OC1

DS

PRESET

VSS

VDD

W.A.R.P.

2.0

LASTIN

MCLK

WAIT

ENDOFL

ERR

OE

AUTO

3

SIS0-SIS2

RD

READY

Figure1. Logic Diagram.

Digital Fuzzy Co-processor 8-bit I/O

HighSpeed Rules Processing

4 Input, 2 Output,32 Rulesin 33.1

μ

s

Upto 256 Rules (4 Antecedents,1 Consequent)

Up to 8Input ConfigurableVariables

Up to 16 MembershipFunctions foran Input

Variable

AntecedentMembership Functions with

Triangular and TrapezoidalShape

Up to 4 Output Variables

Up to 256 Membership Functions for all

Consequents

SingletonConsequentMembership Functions

Defuzzification on chip

Maximum Clock Frequency40MHz

A/D Start Convertion Pulsepresettable

Direct Interfaceto all popular microprocessor

HandshakingSignal Polarity presettable

Operates ”STANDALONE” (without

μ

P) if

desired

Standard+5V SupplyVoltage

SoftwareTools and Emulators Availability

Pinnumber: 52

68-leadPlastic LeadedChip Carrier package.

ANTECEDENT

MEMORY

PROGRAM &

CONSEQUENT

MEMORY

PROGRAMMABLEA/D

OUTPUT PULSE

INTERNALBUS

Input Port

with

HANDSHAKE

8

ALPHA

CALCULATOR

INFERENCE

UNIT

DEFUZZIFIER

Ouput Port

with

HANDSHAKE

8

Figure2. Simplified Block Diagram.

W.A.R.P.2.0

8-BIT FUZZY CO-PROCESSOR

PRELIMINARYDATA

1/28

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W.A.R.P.2.0 | 8-BIT FUZZY CO-PROCESSOR |

| W024400 | VACUUM PIC-UP PEN ESD |

| W0512HD2 | DC to DC Converter |

| W0515GD2 | DC to DC Converter |

| W0515HD2 | DC to DC Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| WARP20 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT FUZZY CO-PROCESSOR |

| WARRANTY REPAIR | 制造商:PREMIER FARNELL 功能描述:WARRANTY REPAIR |

| WARREXT2YR-140 | 制造商:Kontron 功能描述:EXTENDED WARRANTY - Bulk |

| WARR-PVI266-15YR | 制造商:Solectria 功能描述: |

| WARR-PVI95-15YR | 制造商:Solectria 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。